|     | REVISIONS                                                                 |                 |                   |

|-----|---------------------------------------------------------------------------|-----------------|-------------------|

| LTR | DESCRIPTION                                                               | DATE (YR-MO-DA) | APPROVED          |

| А   | Update boilerplate to current MIL-PRF-38535 requirements PHN              | 18-04-16        | Thomas M. Hess    |

| В   | Update boilerplate paragraphs to current VID description requirements PHN | 23-09-18        | Muhammad A. Akbar |

|     |                                                                           |                 |                   |

|     |                                                                           |                 |                   |

|     |                                                                           |                 |                   |

|     |                                                                           |                 |                   |

|     |                                                                           |                 |                   |

Prepared in accordance with ASME Y14.24

Vendor Item Drawing

| Revision State | Revision Status of Sheets |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |  |

|----------------|---------------------------|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|--|

| REV            |                           |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |  |

| SHEET          |                           |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |  |

| REV            |                           |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |  |

| SHEET          |                           |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |  |

| REV            | В                         | В | В | В | В | В | В | В | В | В  | В  | В  | В  | В  | В  | В  | В  | В  | В  | В  | В  |  |

| SHEET          | 1                         | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 |  |

| PMIC N/A                 | PREPARE | ED BY<br>Phu H. Nguyen | DLA LAND AND MARITIME COLUMBUS, OHIO 43218-3990 <a href="https://www.dla.mil/landandmaritime">https://www.dla.mil/landandmaritime</a> |  |  |  |  |

|--------------------------|---------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Original date of drawing | CHECKE  | BY                     | TITLE                                                                                                                                 |  |  |  |  |

| Phu H. Nguyen            |         |                        | MICROCIRCUIT, DIGITAL, MIXED SIGNAL                                                                                                   |  |  |  |  |

| YY MM DD                 | APPROVE | D BY                   | MICROCONTROLLER, MONOLITHIC SILICON                                                                                                   |  |  |  |  |

| 12-12-14                 | Т       | homas M. Hess          |                                                                                                                                       |  |  |  |  |

|                          | SIZE    | CAGE CODE              | DWG NO.                                                                                                                               |  |  |  |  |

|                          | Α       | 16236                  | V62/12620                                                                                                                             |  |  |  |  |

|                          | REV     | В                      | PAGE 1 OF 12                                                                                                                          |  |  |  |  |

AMSC N/A 5962-V155-23

### 1. SCOPE

- 1.1 <u>Scope</u>. This drawing documents the general requirements of a high performance mixed signal microcontroller microcircuit, with an operating temperature range of -40°C to +125°C.

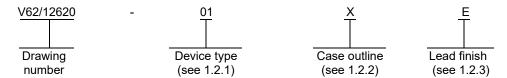

- 1.2 <u>Vendor Item Drawing Administrative Control Number</u>. The manufacturer's PIN is the item of identification. The vendor item drawing establishes an administrative control number for identifying the item on the engineering documentation:

1.2.1 Device type(s).

Device type

Generic

Circuit function

01

MSP430G2230-EP

Mixed signal microcontroller

1.2.2 <u>Case outline(s)</u>. The case outlines are as specified herein.

| Outline letter | Number of pins | JEDEC PUB 95 | Package style         |

|----------------|----------------|--------------|-----------------------|

| X              | 8              | JEDEC MS-012 | Plastic small outline |

1.2.3 Lead finishes. The lead finishes are as specified below or other lead finishes as provided by the device manufacturer:

| inish designator | <u>Material</u>                                                                    |

|------------------|------------------------------------------------------------------------------------|

| Α                | Hot solder dip                                                                     |

| В                | Tin-lead plate                                                                     |

| С                | Gold plate                                                                         |

| D                | Palladium                                                                          |

| E                | Gold flash palladium                                                               |

| F                | Tin-lead alloy                                                                     |

| Z                | Other                                                                              |

| B<br>C<br>D<br>E | Tin-lead plate<br>Gold plate<br>Palladium<br>Gold flash palladiu<br>Tin-lead alloy |

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO | SIZE<br>A |     | GE CODE<br>16236 | DWG NO.<br>V62/12620 |  |

|-----------------------------------------|-----------|-----|------------------|----------------------|--|

|                                         |           | REV | В                | PAGE 2               |  |

## 1.3 Absolute maximum ratings.

| Voltage applied at V <sub>CC</sub> to V <sub>SS</sub> | 0.3 V to 4.1 V |

|-------------------------------------------------------|----------------|

| Voltage applied to any pin                            |                |

| Diode current at any device terminal                  |                |

| Storage temperature: <u>3</u> /                       |                |

| Unprogrammed device                                   | 55°C to 150°C  |

| Programmed device                                     |                |

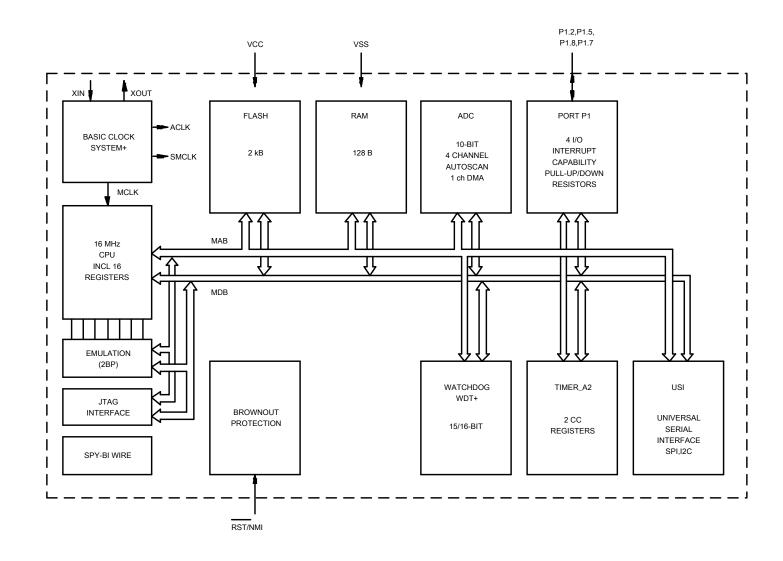

### 1.4 Recommended operating conditions.

| Supply voltage, (V <sub>CC</sub> ):                |                |

|----------------------------------------------------|----------------|

| During program execution                           | 1.8 V to 3.6 V |

| During flash program/erase                         | 2.2 V to 3.6 V |

| Supply voltage, (VSS)                              | . 0 V          |

| Operating free air temperature, (T <sub>A</sub> )  | -40°C to 125°C |

| Processor frequency (Maximum MCLK frequency) 4/ 5/ |                |

| V <sub>CC</sub> = 1.8 V, Duty cycle = 50% ±10%     | dc to 6 MHz    |

| V <sub>CC</sub> = 2.7 V, Duty cycle = 50% ±10%     | dc to 12 MHz   |

| V <sub>CC</sub> = 3.3 V, Duty cycle = 50% ±10%     | dc to 16 MHz   |

#### 2. APPLICABLE DOCUMENTS

## JEDEC - SOLID STATE TECHNOLOGY ASSOCIATION (JEDEC)

JEP95 Registered and Standard Outlines for Semiconductor Devices

J-STD-020 Joint IPC/JEDEC standard for moisture/reflow sensitivity classification for nonhermetic solid state

surface mount devices.

(Copies of these documents are available online at https://www.jedec.org.)

| DLA LAND AND MARITIME | SIZE<br>A |     | GE CODE<br>16236 | DWG NO.<br>V62/12620 |

|-----------------------|-----------|-----|------------------|----------------------|

| COLUMBUS, OHIO        |           | REV | В                | PAGE 3               |

Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

All voltage values referenced to V<sub>SS</sub>. The JTAG fuse blow voltage, V<sub>FB</sub> is allowed to exceed the absolute maximum rating. The voltage is applied to the TEST pin when blowing the JTAG fuse..

Higher temperature may be applied during board soldering according to the current JEDEC J STD 020 specification with peak reflow temperatures not higher than classified on the device label on the shipping boxes or reels.

The MSP430 CPU is clocked directly with MCLK. Both the high and low phase of MCLK must not exceed the pulse width of the specified maximum frequency.

Modules might have different maximum input clock specification. See the specification from the manufacturer data sheet.

#### 3. REQUIREMENTS

- 3.1 <u>Marking</u>. Parts shall be permanently and legibly marked with the manufacturer's part number as shown in 6.3 herein and as follows:

- A. Manufacturer's name, CAGE code, or logo

- B. Pin 1 identifier

- C. ESDS identification (optional)

- 3.2 <u>Unit container</u>. The unit container shall be marked with the manufacturer's part number and with items A and C (if applicable) above.

- 3.3 <u>Electrical characteristics</u>. The maximum and recommended operating conditions and electrical performance characteristics are as specified in 1.3, 1.4, and table I herein.

- 3.4 <u>Design, construction, and physical dimension</u>. The design, construction, and physical dimensions are as specified herein.

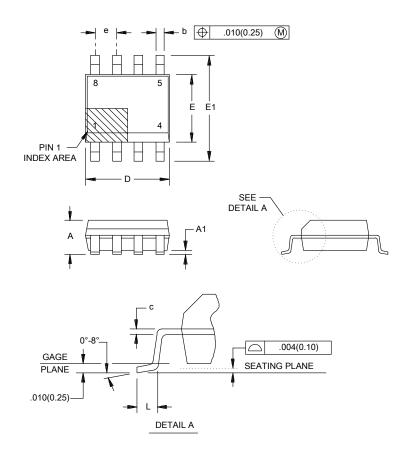

- 3.5 Diagrams.

- 3.5.1 Case outline. The case outline shall be as shown in 1.2.2 and figure 1.

- 3.5.2 <u>Terminal connections</u>. The terminal connections shall be as shown in figure 2.

- 3.5.3 Terminal function. The terminal function shall be as shown in figure 3.

- 3.5.4 Functional block diagram. The functional block diagram shall be as shown in figure 4.

- 3.5.5 <u>Safe operating area</u>. The safe operating area shall be as shown in figure 5.

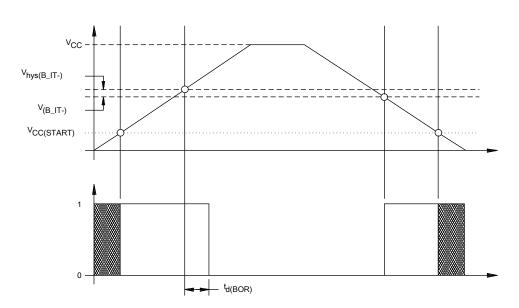

- 3.5.6 POR/Brownout Reset (BOR) vs Supply voltage. The POR/Brownout Reset (BOR) vs Supply voltage shall be as shown in figure 6.

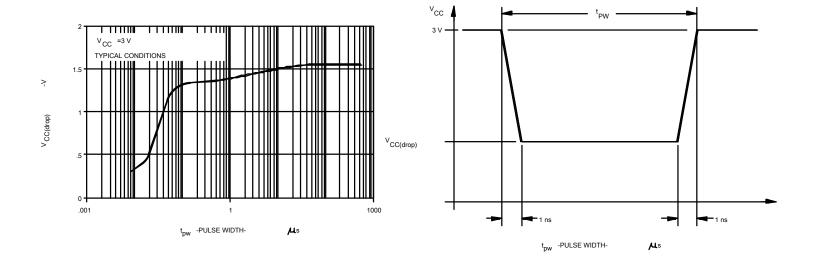

- 3.5.7 V<sub>CC(drop)</sub> level with a Square voltage drop to gernerate a POR/Brownout signal. The V<sub>CC(drop)</sub> level with a Square voltage drop to gernerate a POR/Brownout signal shall be as shown in figure 7.

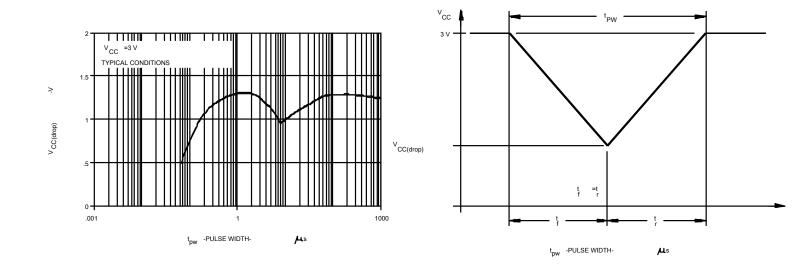

- 3.5.8 V<sub>CC(drop)</sub> level with a Triangle voltage drop to gernerate a POR/Brownout signal. The V<sub>CC(drop)</sub> level with a Triangle voltage drop to gernerate a POR/Brownout signal shall be as shown in figure 8.

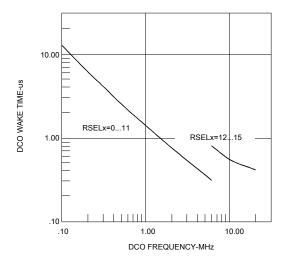

- 3.5.9 <u>DCO wake-up time from LPM3/4 vs DCO frequency</u>. The DCO wake-up time from LPM3/4 vs DCO frequency waveforms shall be as shown in figure 9.

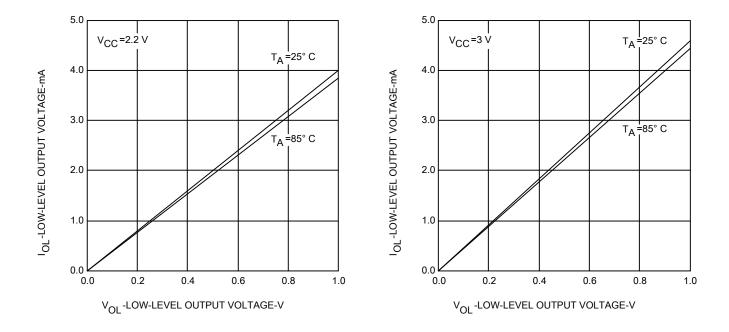

- 3.5.10 <u>USI low level output voltage vs output current</u>. The USI low level output voltage vs output current shall be as shown in figure 10.

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO | SIZE<br>A | CAGE<br>162 | _ | DWG NO.<br>V62/12620 |  |

|-----------------------------------------|-----------|-------------|---|----------------------|--|

|                                         |           | REV         | В | PAGE 4               |  |

TABLE I. Electrical performance characteristics.  $\underline{1}/$

| Test                               | Symbol                  | Conditions                                                                                                                                                                                      | TA    | Vcc   | Lim | its | Unit |

|------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-----|-----|------|

|                                    |                         | <u>2</u> /                                                                                                                                                                                      |       |       | Min | Max |      |

| Active mode supply curre           | nt into Vcc ex          | cluding external current                                                                                                                                                                        |       |       |     |     |      |

| Active mode (AM) current (1 MHz)   | I <sub>AM</sub> , 1MHz  | f <sub>DCO</sub> = f <sub>MCLK</sub> = 1 MHz,<br>f <sub>ACLK</sub> = 0 Hz,<br>Program executes in flash,                                                                                        |       | 2.2 V | 220 | TYP | μA   |

|                                    |                         | BCSCTL1 = CALBC1_1MHz,<br>DCOCTL = CALDCO_1MHz,<br>CPUOFF = 0, SCG0 = 0<br>SCG1 = 0, OSCOOFF = 0                                                                                                |       | 3 V   |     | 390 | μА   |

| Low power mode Supply o            | urrent (into            | V <sub>CC</sub> ) Excluding external current                                                                                                                                                    |       |       |     |     | -    |

| Low power mode 0 (LPM0) current    | ILPMO, 1MHz             | $f_{MCLK} = 0$ MHz,<br>$f_{SMCLK} = f_{CDO} = 1$ MHz,<br>$f_{ACLK} = 32,768$ Hz,<br>$BCSCTL1 = CALBC1_1MHz$ ,<br>$DCOCTL = CALDCO_1MHz$ ,<br>CPUOFF = 1, $SCG0 = 0$ ,<br>SCG1 = 1, $OSCOFF = 0$ | 25°C  | 2.2 V | 65  | TYP | μА   |

| Low power mode 2 (LPM2) current    | I <sub>LPM2</sub>       | $f_{MCLK} = f_{SMCLK} = 0 \text{ MHz},$ $f_{CDO} = 1 \text{ MHz},$ $f_{ACLK} = 32,768 \text{ Hz},$ $BCSCTL1 = CALBC1_1MHz,$                                                                     | 25°C  | 2.2 V |     | 29  | μА   |

|                                    |                         | DCOCTL = CALDCO_1MHz,<br>CPUOFF = 1, SCG0 = 0,<br>SCG1 = 1, OSCOFF = 0                                                                                                                          | 125°C |       |     | 46  | μА   |

| Low power mode 3 (LPM3) current    | I <sub>L</sub> PM3, VLO | f <sub>DCO</sub> = f <sub>MCLK</sub> = f <sub>SMCLK</sub> = 0 MHz,<br>f <sub>ACLK</sub> = from internal LF oscillator<br>(VLO),<br>CPUOFF = 1, SCG0 = 1,                                        | 25°C  | 2.2 V |     | 0.7 | μА   |

|                                    |                         | SCG1 = 1, OSCOFF = 0                                                                                                                                                                            | 125°C |       |     | 9.3 | μA   |

| Low power mode 4<br>(LPM4) current | I <sub>LPM4</sub>       | $f_{DCO} = f_{MCLK} = f_{SMCLK} = 0 \text{ MHz},$<br>$f_{ACLK} = 0 \text{ Hz},$<br>CPUOFF = 1, SCG0 = 1,                                                                                        | 25°C  | 2.2 V |     | 0.5 | μА   |

| <u>5</u> /                         |                         | SCG1 = 1, OSCOFF = 1                                                                                                                                                                            | 85°C  |       |     | 1.5 | μA   |

|                                    |                         | $T_A$ = 125°C<br>$f_{DCO}$ = $f_{MCLK}$ = $f_{SMCLK}$ = 0 MHz,<br>$f_{ACLK}$ = 0 Hz,<br>CPUOFF = 1, SCG0 = 1,<br>SCG1 = 1, OSCOFF = 1                                                           |       | 2.2 V |     | 7.1 | μА   |

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO | SIZE<br>A |     | E CODE<br>6236 | DWG NO.<br>V62/12620 |  |

|-----------------------------------------|-----------|-----|----------------|----------------------|--|

|                                         |           | REV | В              | PAGE 5               |  |

TABLE I. Electrical performance characteristics - Continued.  $\underline{1}/$

| Test                                                            | Symbol                  | Conditions                                                                                       | Vcc | Lim                           | its                  | Unit |  |

|-----------------------------------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------|-----|-------------------------------|----------------------|------|--|

|                                                                 |                         | <u>2</u> /                                                                                       |     | Min                           | Max                  |      |  |

| Schmitt Trigger inputs (Port P1)                                |                         | 1                                                                                                |     |                               |                      |      |  |

| Positive going input threshold                                  | V <sub>IT+</sub>        |                                                                                                  |     | 0.45 V <sub>CC</sub>          | $0.75\ V_{CC}$       | V    |  |

| voltage                                                         |                         |                                                                                                  | 3 V | 1.35                          | 2.25                 | V    |  |

| Negative going input threshold                                  | V <sub>IT</sub> -       |                                                                                                  |     | 0.25 V <sub>CC</sub>          | 0.55 V <sub>CC</sub> | V    |  |

| voltage                                                         |                         |                                                                                                  | 3 V | 0.75                          | 1.65                 | V    |  |

| Input voltage hysteresis (V <sub>IT+</sub> - V <sub>IT-</sub> ) | V <sub>hys</sub>        |                                                                                                  | 3 V | 0.3                           | 1.0                  | V    |  |

| Pullup/pulldown resistor                                        | R <sub>Pull</sub>       | For pullup: V <sub>IN</sub> = V <sub>SS</sub><br>For pulldown: V <sub>IN</sub> = V <sub>CC</sub> |     | 20                            | 50                   | kΩ   |  |

| Input capacitance                                               | Cı                      | V <sub>IN</sub> = V <sub>SS</sub> or V <sub>CC</sub>                                             |     | 5                             | TYP                  | pF   |  |

| Leakage current (Port P1)                                       |                         |                                                                                                  |     |                               |                      |      |  |

| High impedance leakage current                                  | I <sub>lkg(Px.y)</sub>  | <u>6</u> / <u>7</u> /                                                                            | 3 V |                               | ±120                 | nA   |  |

| Outputs (Port P1)                                               |                         |                                                                                                  |     |                               |                      |      |  |

| High level output voltage                                       | V <sub>OH</sub>         | I <sub>(OHmax)</sub> = -6 mA <u>8/</u>                                                           | 3 V | $V_{CC} - 0.3$                | TYP                  | V    |  |

| Low level output voltage                                        | Vol                     | $I_{(OLmax)} = 6 \text{ mA } 8/$                                                                 | 3 V | Vss + 0.3                     | TYP                  | V    |  |

| Output frequency (Port P1)                                      | •                       |                                                                                                  |     |                               |                      |      |  |

| Port output frequency (with load)                               | f <sub>Px.y</sub>       | $C_L = 20 \text{ pF}, R_L = 1 \text{ k}\Omega \frac{9}{10}$                                      | 3 V | 12                            | TYP                  | MHz  |  |

| Clock output frequency                                          | f <sub>Port°CLK</sub>   | C <sub>L</sub> = 20 pF <u>10</u> /                                                               | 3 V | 16                            | TYP                  | MHz  |  |

| POR/Brownout reset (BOR) 11/                                    |                         |                                                                                                  |     |                               |                      |      |  |

| See figure 10                                                   | V <sub>CC(start)</sub>  | dV <sub>CC</sub> /dt ≤ 3 V/s                                                                     |     | 0.7 x<br>V <sub>(B_IT-)</sub> | TYP                  | V    |  |

| See figure 10 through figure 12                                 | $V_{(B\_IT-)}$          | dV <sub>CC</sub> /dt ≤ 3 V/s                                                                     |     |                               | 1                    | V    |  |

| See figure 10                                                   | V <sub>hys(B_IT-)</sub> | dV <sub>CC</sub> /dt ≤ 3 V/s                                                                     |     | 140                           | TYP                  | mV   |  |

| See figure 10                                                   | t <sub>d(BOR)</sub>     | 34/                                                                                              |     |                               | 2000                 | μs   |  |

| Pulse length needed at RST/NMI pin to accept reset internally   | t <sub>(reset)</sub>    | 34/                                                                                              | 3 V | 2                             |                      | μs   |  |

| DLA LAND AND MARITIME | SIZE<br>A |     | E CODE<br>6236 | DWG NO.<br>V62/12620 |

|-----------------------|-----------|-----|----------------|----------------------|

| COLUMBUS, OHIO        |           | REV | В              | PAGE 6               |

TABLE I. Electrical performance characteristics - Continued.  $\underline{1}/$

| Test                                           | Symbol                       | Conditions                                                                   | Vcc | Lir   | mits | Unit  |

|------------------------------------------------|------------------------------|------------------------------------------------------------------------------|-----|-------|------|-------|

|                                                | <u>2</u> /                   |                                                                              |     | Min   | Max  |       |

| DCO frequency                                  | ,                            |                                                                              |     | T     |      |       |

|                                                |                              | RSELx < 14                                                                   |     | 1.8   | 3.6  | V     |

| Supply voltage                                 | Vcc                          | RSELx = 14                                                                   |     | 2.2   | 3.6  | V     |

|                                                |                              | RSELx = 15                                                                   |     | 3.0   | 3.6  | V     |

| DCO frequency (0, 0)                           | f <sub>DCO(0,0)</sub>        | RSELx = 0, $DCOx = 0$ , $MDDx = 0$                                           | 3 V | 0.096 | TYP  | MHz   |

| DCO frequency (0, 3)                           | f <sub>DCO(0,3)</sub>        | RSELx = 0, $DCOx = 3$ , $MDDx = 0$                                           | 3 V | 0.12  | TYP  | MHz   |

| DCO frequency (1, 3)                           | f <sub>DCO(1,3)</sub>        | RSELx = 1, $DCOx = 3$ , $MDDx = 0$                                           | 3 V | 0.15  | TYP  | MHz   |

| DCO frequency (2, 3)                           | f <sub>DCO(2,3)</sub>        | RSELx = 2, $DCOx = 3$ , $MDDx = 0$                                           | 3 V | 0.21  | TYP  | MHz   |

| DCO frequency (3, 3)                           | <b>f</b> <sub>DCO(3,3)</sub> | RSELx = 3, $DCOx = 3$ , $MDDx = 0$                                           | 3 V | 0.30  | TYP  | MHz   |

| DCO frequency (4, 3)                           | f <sub>DCO(4,3)</sub>        | RSELx = 4, DCOx = 3, MDDx = 0                                                | 3 V | 0.41  | TYP  | MHz   |

| DCO frequency (5, 3)                           | f <sub>DCO(5,3)</sub>        | RSELx = 5, $DCOx = 3$ , $MDDx = 0$                                           | 3 V | 0.58  | TYP  | MHz   |

| DCO frequency (6, 3)                           | f <sub>DCO(6,3)</sub>        | RSELx = 6, $DCOx = 3$ , $MDDx = 0$                                           | 3 V | 0.80  | TYP  | MHz   |

| DCO frequency (7, 3)                           | f <sub>DCO(7,3)</sub>        | RSELx = 7, DCOx = 3, MDDx = 0                                                | 3 V | 0.80  | 1.50 | MHz   |

| DCO frequency (8, 3)                           | f <sub>DCO(8,3)</sub>        | RSELx = 8, $DCOx = 3$ , $MDDx = 0$                                           | 3 V | 1.6   | TYP  | MHz   |

| DCO frequency (9, 3)                           | <b>f</b> DCO(9,3)            | RSELx = 9, $DCOx = 3$ , $MDDx = 0$                                           | 3 V | 2.3   | TYP  | MHz   |

| DCO frequency (10, 3)                          | f <sub>DCO(10,3)</sub>       | RSELx = 10, DCOx = 3, MDDx = 0                                               | 3 V | 3.4   | TYP  | MHz   |

| DCO frequency (11, 3)                          | f <sub>DCO(11,3)</sub>       | RSELx = 11, DCOx = 3, MDDx = 0                                               | 3 V | 4.25  | TYP  | MHz   |

| DCO frequency (12, 3)                          | f <sub>DCO(12,3)</sub>       | RSELx = 12, DCOx = 3, MDDx = 0                                               | 3 V | 4.3   | 7.30 | MHz   |

| DCO frequency (13, 3)                          | f <sub>DCO(13,3)</sub>       | RSELx = 13, DCOx = 3, MDDx = 0                                               | 3 V | 7.8   | TYP  | MHz   |

| DCO frequency (14, 3)                          | f <sub>DCO(14,3)</sub>       | RSELx = 14, DCOx = 3, MDDx = 0                                               | 3 V | 8.6   | 13.9 | MHz   |

| DCO frequency (15, 3)                          | f <sub>DCO(15,3)</sub>       | RSELx = = 15, DCOx = 3, MDDx = 0                                             | 3 V | 15.25 | TYP  | MHz   |

| DCO frequency (15, 7)                          | f <sub>DCO(15,7)</sub>       | RSELx = 15, DCOx = 7, MDDx = 0                                               | 3 V | 21    | TYP  | MHz   |

| Frequency step between range RSEL and RSEL + 1 | S <sub>RESL</sub>            | S <sub>RSEL</sub> = f <sub>DCO(RSEL+1,DCO)</sub> /f <sub>DCO(RSEL,DCO)</sub> | 3 V | 1.35  | TYP  | ratio |

| Frequency step between tap DCO and DCO + 1     | S <sub>DCO</sub>             | $S_{DCO} = f_{DCO(RSEL,DCO+1)}/f_{DCO(RSEL,DCO)}$                            | 3 V | 1.08  | TYP  | ratio |

| Duty cycle                                     |                              |                                                                              | 3 V | 50    | TYP  | %     |

| DLA LAND AND MARITIME | SIZE<br>A |     | SE CODE<br>16236 | DWG NO.<br>V62/12620 |

|-----------------------|-----------|-----|------------------|----------------------|

| COLUMBUS, OHIO        |           | REV | В                | PAGE 7               |

TABLE I. Electrical performance characteristics - Continued.  $\underline{1}/$

| Test                                  | Conditions                      | TA             | Vcc        | Lin | Unit |   |

|---------------------------------------|---------------------------------|----------------|------------|-----|------|---|

|                                       | <u>2</u> /                      |                |            | Min | Max  |   |

| Calibrated DCO frequencies            | - Tolerance over temperature -4 | 0°C to 125°C   |            |     |      |   |

| •                                     | BCSCTL1 = CALBC1_1MHz,          | -40°C to 125°C | 3 V        | -3  | 3    | % |

| 1 MHz tolerance over                  | DCOCTL = CALDCO_1MHz,           |                |            |     |      |   |

| temperature                           | calibrated at 30°C and 3 V      |                |            |     |      |   |

|                                       | BCSCTL1 = CALBC1_8MHz,          | -40°C to 125°C | 3 V        | -3  | 3    | % |

| 8 MHz tolerance over                  | DCOCTL = CALDCO_8MHz,           |                |            |     |      |   |

| temperature                           | calibrated at 30°C and 3 V      |                |            |     |      |   |

|                                       | BCSCTL1 = CALBC1_12MHz,         | -40°C to 125°C | 3 V        | -3  | 3    | % |

| 12 MHz tolerance over                 | DCOCTL = CALDCO_12MHz,          |                |            |     |      |   |

| temperature                           | calibrated at 30°C and 3 V      |                |            |     |      |   |

|                                       | BCSCTL1 = CALBC1_16MHz,         | -40°C to 125°C | 3 V        | -3  | 3    | % |

| 16 MHz tolerance over                 | DCOCTL = CALDCO_16MHz,          |                |            |     |      |   |

| temperature                           | calibrated at 30°C and 3 V      |                |            |     |      |   |

| Calibrated DCO frequencies            | - Tolerance over supply voltage | Vcc            | -          |     |      |   |

|                                       | BCSCTL1 = CALBC1_1MHz,          | 25°C           | 1.8 V to   | -3  | 3    | % |

| 1 MHz tolerance over V <sub>CC</sub>  | DCOCTL = CALDCO_1MHz,           |                | 3.6 V      |     |      |   |

|                                       | calibrated at 30°C and 3 V      |                |            |     |      |   |

|                                       | BCSCTL1 = CALBC1_8MHz,          | 25°C           | 1.8 V to   | -3  | 3    | % |

| 8 MHz tolerance over V <sub>CC</sub>  | DCOCTL = CALDCO_8MHz,           |                | 3.6 V      |     |      |   |

|                                       | calibrated at 30°C and 3 V      |                |            |     |      |   |

|                                       | BCSCTL1 = CALBC1_12MHz,         | 25°C           | 2.2 V to   | -3  | 3    | % |

| 12 MHz tolerance over V <sub>CC</sub> | DCOCTL = CALDCO_12MHz,          |                | 3.6 V      |     |      |   |

|                                       | calibrated at 30°C and 3 V      |                |            |     |      |   |

|                                       | BCSCTL1 = CALBC1_16MHz,         | 25°C           | 3 V to 3.6 | -6  | 3    | % |

| 16 MHz tolerance over V <sub>CC</sub> | DCOCTL = CALDCO_16MHz,          |                | V          |     |      |   |

|                                       | calibrated at 30°C and 3 V      |                |            |     |      |   |

| Calibrated DCO frequencies            | - Overall tolerance             |                |            |     |      |   |

|                                       | BCSCTL1 = CALBC1_1MHz,          | -40°C to 85°C  | 1.8 V to   | -5  | +5   | % |

| 1 MHz tolerance overall               | DCOCTL = CALDCO_1MHz,           |                | 3.6 V      |     |      |   |

|                                       | calibrated at 30°C and 3 V      |                |            |     |      |   |

|                                       | BCSCTL1 = CALBC1_8MHz,          | -40°C to 85°C  | 1.8 V to   | -5  | +5   | % |

| 8 MHz tolerance overall               | DCOCTL = CALDCO_8MHz,           |                | 3.6 V      |     |      |   |

|                                       | calibrated at 30°C and 3 V      |                |            |     |      |   |

|                                       | BCSCTL1 = CALBC1_12MHz,         | -40°C to 85°C  | 2.2 V to   | -5  | +5   | % |

| 12 MHz tolerance overall              | DCOCTL = CALDCO_12MHz,          |                | 3.6 V      |     |      |   |

|                                       | calibrated at 30°C and 3 V      |                |            |     |      |   |

|                                       | BCSCTL1 = CALBC1_16MHz,         | -40°C to 85°C  | 3.0 V to   | -6  | +6   | % |

| 16 MHz tolerance overall              | DCOCTL = CALDCO_16MHz,          |                | 3.6 V      |     |      |   |

|                                       | calibrated at 30°C and 3 V      |                |            |     |      |   |

| DLA LAND AND MARITIME | SIZE<br>A |     | SE CODE<br>16236 | DWG NO.<br>V62/12620 |

|-----------------------|-----------|-----|------------------|----------------------|

| COLUMBUS, OHIO        |           | REV | В                | PAGE 8               |

TABLE I. Electrical performance characteristics - Continued.  $\underline{1}/$

| Test                                          | Symbol                              | Conditions                                                                          | Vcc               | Lir                                               | mits                  | Unit |

|-----------------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------|-------------------|---------------------------------------------------|-----------------------|------|

|                                               |                                     | <u>2</u> /                                                                          |                   | Min                                               | Max                   |      |

| Wake up from Lower Power Mo                   | dels (LPM3/4                        | 9)                                                                                  |                   |                                                   |                       |      |

| DCO clock wake up time from LPM3/4            | t <sub>DCO,LPM3/4</sub>             | BCSCTL1 = CALBC1_1MHz,<br>DCOCTL = CALDCO_1MHz,                                     | 2.2 V/ 3 V        | 2                                                 | TYP                   | μs   |

| <u>12</u> /                                   |                                     | BCSCTL1 = CALBC1_8MHz,<br>DCOCTL = CALDCO_8MHz,                                     |                   | 1.5                                               | TYP                   | μs   |

|                                               |                                     | BCSCTL1 = CALBC1_12MHz,<br>DCOCTL = CALDCO_12MHz,                                   |                   | 1                                                 | TYP                   | μs   |

|                                               |                                     | BCSCTL1 = CALBC1_16MHz,<br>DCOCTL = CALDCO_16MHz,                                   | 3 V               | 1                                                 | TYP                   | μs   |

| CPU wake up time from LPM3/4 13/              | tcpu,lpm3/4                         |                                                                                     |                   | 1 / f <sub>MCLK</sub> + t <sub>Clock,LPM3/4</sub> | TYP                   | μs   |

| Internal Very Low power Low f                 | equency Osc                         | 1                                                                                   | ı                 |                                                   | T                     | 1    |

| VLO frequency                                 | f <sub>VLO</sub>                    | $T_A = -40$ °C to 85°C                                                              | 3 V               | 4                                                 | 20                    | kHz  |

|                                               |                                     | T <sub>A</sub> = 125°C                                                              |                   |                                                   | 23                    |      |

| VLO frequency temperature drift 14/           | df <sub>VLO</sub> /d <sub>T</sub>   | T <sub>A</sub> = -40°C to 85°C                                                      | 3 V               | 0.5 TYP                                           |                       | %/°C |

| VLO frequency supply voltage drift <u>15/</u> | df <sub>VLO</sub> /dV <sub>CC</sub> | T <sub>A</sub> = 25°C                                                               | 1.8 V to<br>3.6 V | 4 TYP                                             |                       | %/V  |

| Timer_A                                       | T                                   | T                                                                                   | I                 |                                                   |                       | 1    |

| Timer_A clock frequency                       | f <sub>TA</sub>                     | Internal: SMCLK External: TACLK, INCLK Duty cycle = 50% ±10%                        |                   | fsystem                                           | TYP                   | MHz  |

| Timer_A capture timing                        | f <sub>TA,cap</sub>                 | TAx                                                                                 | 3 V               | 20                                                |                       | ns   |

| USI, Universal Serial Interface               |                                     |                                                                                     | I                 | · ·                                               | I                     |      |

| USI clock frequency                           | fusi                                | External: SCLK, Duty cycle = 50% ±10% SPI slave mode USI module in I <sup>2</sup> C |                   | f <sub>SYSTEM</sub>                               | TYP                   | MHz  |

| Loe level output voltage on SDA and SCL       | V <sub>OL,I2C</sub>                 | mode,<br>I <sub>(OLmax)</sub> = 1.5 mA                                              | 3 V               | V <sub>SS</sub>                                   | V <sub>SS</sub> + 0.4 | V    |

| DLA LAND AND MARITIME | SIZE<br>A |     | E CODE<br>6236 | DWG NO.<br>V62/12620 |

|-----------------------|-----------|-----|----------------|----------------------|

| COLUMBUS, OHIO        |           | REV | В              | PAGE 9               |

TABLE I. Electrical performance characteristics - Continued.  $\underline{1}/$

| Test                                                  | Symbol             | ymbol Conditions                                                                                             |     | Lim  | its | Unit |  |

|-------------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------|-----|------|-----|------|--|

|                                                       | <u>2</u> /         |                                                                                                              |     | Min  | Max |      |  |

| 10 Bit ADC, Power supply and                          | l input rang       | e conditions                                                                                                 |     |      |     |      |  |

| Analog supply voltage                                 | V <sub>CC</sub>    | V <sub>SS</sub> = 0                                                                                          |     | 2.2  | 3.6 | V    |  |

| Analog input voltage 17/                              | VAx                | All Ax terminal, Analog inputs selected in ADC10AE register                                                  | 3 V | 0    | Vcc | V    |  |

| ADC10 supply current 18/                              | I <sub>ADC10</sub> | f <sub>ADC10CLK</sub> = 5.0 MHz,<br>ADC10ON = 1, REFON = 0,<br>ADC10SHT0 = 1, ADC10SHT1 = 0,<br>ADC10DIV = 0 | 3 v | 0.6  | TYP | mA   |  |

| Reference supply current, reference buffer disabled   | I <sub>REF+</sub>  | f <sub>ADC10CLK</sub> = 5.0 MHz,<br>ADC10ON = 0, REF2_5V = 0,<br>REFON = 1, REFOUT = 0                       | 3 V | 0.25 | TYP | mA   |  |

| <u>19</u> /                                           |                    | f <sub>ADC10CLK</sub> = 5.0 MHz,<br>ADC10ON = 0, REF2_5V = 1,<br>REFON = 1, REFOUT = 0                       | 3 v | 0.25 | TYP | mA   |  |

| Reference buffer supply current with ADC10SR = 0  19/ | IREFB,0            | f <sub>ADC10CLK</sub> = 5.0 MHz,<br>ADC10ON = 0, REFON = 1,<br>REF2_5V = 0, REFOUT = 1,<br>ADC10SR = 0       | 3 V | 1.1  | TYP | mA   |  |

| Reference buffer supply current with ADC10SR = 1      | IREFB,1            | fadc10CLK = 5.0 MHz, 3 v 0.5<br>ADC10ON = 0, REFON = 0,<br>REF2_5V = 0, REFOUT = 1,<br>ADC10SR = 1           |     | TYP  | mA  |      |  |

| Input capacitance                                     | Cı                 |                                                                                                              |     | 27   | pF  |      |  |

| Input MUX ON resistance                               | Rı                 | 0 V ≤ V <sub>AX</sub> ≤ V <sub>CC</sub>                                                                      | 3 v | 1000 | TYP | Ω    |  |

| DLA LAND AND MARITIME | SIZE<br>A |     | E CODE<br>6236 | DWG NO.<br>V62/12620 |

|-----------------------|-----------|-----|----------------|----------------------|

| COLUMBUS, OHIO        |           | REV | В              | PAGE 10              |

TABLE I. Electrical performance characteristics - Continued.  $\underline{1}/$

| Test                                                                          | Symbol                | Symbol Conditions                                                                                                            |       | Vcc Limits |      |       |

|-------------------------------------------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------|-------|------------|------|-------|

|                                                                               | <u>2</u> /            |                                                                                                                              |       | Min        | Max  |       |

| 0 bit ADC, Built in voltage reference                                         | <u>35</u> /           | 1                                                                                                                            |       |            | T    | 1     |

| Positive built in reference analog                                            | V <sub>CC, REF+</sub> | $I_{VREF+} \le 1 \text{ mA}, REF2\_5V = 0$                                                                                   |       | 2.2        |      | V     |

| supply voltage range                                                          |                       | I <sub>VREF+</sub> ≤ 1 mA, REF2_5V = 1                                                                                       |       | 3.0        |      | V     |

| Positive built in reference voltage                                           | V <sub>REF+</sub>     | $I_{VREF+} \le I_{VREF+} \max, REF2_5V = 0$                                                                                  | 3 V   | 1.4        | 1.59 | V     |

|                                                                               |                       | I <sub>VREF+</sub> ≤ I <sub>VREF+</sub> max, REF2_5V = 1                                                                     |       | 2.34       | 2.65 | V     |

| Maximum V <sub>REF+</sub> load current                                        | I <sub>LD,VREF+</sub> | <u>34</u> /                                                                                                                  | 3 V   |            | ±1   | mA    |

| VREF+ load regulation                                                         |                       | $I_{VREF+}$ = 500 μA ±100 μA,<br>Analog input voltage $V_{Ax} \neq 0.75$ V,<br>REF2_5V = 0                                   | 3 V   |            | ±2   | LSB   |

|                                                                               |                       | $I_{VREF+}$ = 500 μA ±100 μA<br>Analog input voltage $V_{Ax} \neq 1.25$ V,<br>REF2_5V = 1                                    |       |            | ±2   | LSB   |

| VREF+ load regulation response time                                           |                       | $I_{VREF+}$ = 100 μA $\rightarrow$ 900 μA<br>$V_{AX} \neq 0.5$ V x VREF+,<br>Error conversion result ≤ 1 LSB,<br>ADC10SR = 0 | 3 V   |            | 400  | ns    |

| Maximum capacitance at pin VREF+                                              | C <sub>VREF+</sub>    | I <sub>VREF+</sub> ≤ 1 mA, REFON = 1, REFOUT = 1                                                                             | 3 V   |            | 100  | pF    |

| Temperature coefficient                                                       | TC <sub>REF+</sub>    | $I_{VREF+}$ = const with 0 mA $\leq I_{VREF+} \leq 1$ mA                                                                     | 3 V   |            | ±190 | ppm/° |

| Setting time of internal reference voltage to 99.9% VREF                      | t <sub>REFON</sub>    | $I_{VREF+} = 0.5 \text{ mA}, REF2\_5V = 0,$<br>REFON = 0 \rightarrow 1                                                       | 3.6 V |            | 30   | μs    |

| Setting time of reference buffer to 99.9% VREF                                | t <sub>REFBURST</sub> | I <sub>VREF+</sub> = 0.5 mA,<br>REF2_5V = 1, REFON = 1<br>REFBURST = 1, ADC10SR = 0                                          | 3 V   |            | 2    | μs    |

| 10 Bit ADC, External reference 20                                             | / <u>36</u> /         | ,                                                                                                                            |       |            | l .  |       |

| Positive external reference input                                             | VEREF+                | VEREF+ > VEREF-,<br>SREF1 = 1, SREF0 = 0                                                                                     |       | 1.4        | Vcc  | V     |

| voltage range <u>21</u> /                                                     |                       | VEREF- ≤ VEREF+ ≤ V <sub>CC</sub> – 0.15 V,<br>SREF1 = 1, SREF0 = 1 22/                                                      |       | 1.4        | 3    | V     |

| Negative external reference input voltage range 23/                           | VEREF-                | VEREF+ > VEREF-                                                                                                              |       | 0          | 1.2  | V     |

| Differential external reference input voltage range, ΔVEREF = VEREF+ - VEREF- | ΔVEREF                | VEREF+ > VEREF- <u>24</u> /                                                                                                  |       | 1.4        | Vcc  | V     |

| Static input current into VEREF+                                              | I <sub>VEREF+</sub>   | $0 \text{ V} \le \text{VEREF+} \le \text{V}_{\text{CC}} - 0.15 \text{ V} \le 3 \text{ V},$<br>SREF1 = 1, SREF0 = 0           | 3 V   | ±1         | TYP  | μΑ    |

|                                                                               |                       | $0 \text{ V} \le \text{VEREF+} \le \text{V}_{CC} - 0.15 \text{ V} \le 3 \text{ V},$<br>SREF1 = 1, SREF0 = 1 $22$ /           | 3 V   | 0          | TYP  | μΑ    |

| Static input current into VEREF-                                              | Iveref-               | 0 V ≤ VEREF- ≤ V <sub>CC</sub>                                                                                               | 3 V   | ±1         | TYP  | μA    |

| DLA LAND AND MARITIME | SIZE<br>A |     | E CODE<br>6236 | DWG NO.<br>V62/12620 |

|-----------------------|-----------|-----|----------------|----------------------|

| COLUMBUS, OHIO        |           | REV | В              | PAGE 11              |

TABLE I. Electrical performance characteristics - Continued.  $\underline{1}/$

| Test                                               | Symbol                     | Conditions                                                      |                 | Vcc  | Lir                                | nits        | Unit  |

|----------------------------------------------------|----------------------------|-----------------------------------------------------------------|-----------------|------|------------------------------------|-------------|-------|

|                                                    | <u>2</u> /                 |                                                                 |                 | Min  | Max                                |             |       |

| 10 Bit ADC, Timing parameters                      | <u>36</u> /                |                                                                 |                 |      |                                    |             |       |

| ADC10 input clock frequency                        | f <sub>ADC10CLK</sub>      | For specified                                                   | ADC10SR = 0     | 3 V  | 0.45                               | 6.3         | MHz   |

|                                                    |                            | performance of ADC10 linearity parameters                       | ADC10SR = 1     |      | 0.45                               | 1.5         | MHz   |

| ADC10 built in oscillator frequency                | f <sub>ADC100SC</sub>      | ADC10DIVx = 0, ADC10SS<br>fADC10CLK = fADC10OSC                 | SELx = 0,       | 3 V  | 3.7                                | 6.3         | MHz   |

| Conversion time                                    | tconvert                   | ADC10 built in oscillator, A fADC10CLK = fADC10OSC              | DC10SSELx = 0,  | 3 V  | 2.06                               | 3.51        | μs    |

|                                                    |                            | f <sub>ADC10CLK</sub> from ACLK, MCLI<br>ADC10SSELx ≠ 0         | K, or SMCLK:    |      | 13 x AD0<br>1/f <sub>ADC10CL</sub> | C10DIV x    | μs    |

| Turn on setting time of the ADC                    | tadc100N                   | <u>25</u> /                                                     |                 |      |                                    | 100         | ns    |

| 10 Bit ADC, Linearity parameters                   | <u>36</u> /                |                                                                 |                 |      |                                    |             |       |

| Integral linearity error                           | Eı                         |                                                                 |                 | 3 V  |                                    | ±1          | LSB   |

| Differential linearity error                       | E <sub>D</sub>             |                                                                 | 3 V             |      | ±1                                 | LSB         |       |

| Offset error                                       | Eo                         | Source impedance Rs < 10                                        | 3 V             |      | ±1                                 | LSB         |       |

| Gain error                                         | E <sub>G</sub>             |                                                                 |                 | 3 V  |                                    | ±2          | LSB   |

| Total unadjusted error                             | Ет                         |                                                                 |                 | 3 V  |                                    | ±5          | LSB   |

| 10 Bit ADC, Temperature sensor                     | and built in               | V <sub>MID</sub> <u>36</u> /                                    |                 |      | •                                  |             |       |

| Temperature sensor supply current 26/              | I <sub>SENSOR</sub>        | REFON = 0, INCHx = $0A$<br>T <sub>A</sub> = $25^{\circ}$ C      | Ah,             | 3 V  | 60                                 | TYP         | μA    |

|                                                    | TC <sub>SENSOR</sub>       | ADC10ON = 1 INCHx =                                             | 0Ah <u>27</u> / | 3 V  | 3.55                               | TYP         | mV/°C |

| Sample time required if channel 10 is selected 28/ | t <sub>Sensor(sample</sub> | ADC10ON = 1 INCHx = Error of conversion resul                   | - ,             | 3 V  | 30                                 |             | μs    |

| Current into divider at channel 11                 | I <sub>VMID</sub>          | ADC10ON = 1 INCHx =                                             | 0Bh             | 3 V  |                                    | <u>29</u> / | μA    |

| V <sub>CC</sub> divider at channel 11              | V <sub>MID</sub>           | ADC10ON = 1 INCHx =<br>V <sub>MID</sub> ≠ 0.5 x V <sub>CC</sub> | 3 V             | 1.5  | TYP                                | V           |       |

| Sample time required if channel 11 is selected 30/ | tvMID(sample               | ADC10ON = 1 INCHx = Error of conversion resul                   | 3 V             | 1220 |                                    | ns          |       |

| RAM                                                |                            |                                                                 |                 |      |                                    |             | -     |

|                                                    |                            |                                                                 |                 |      |                                    |             |       |

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO | SIZE<br>A | CAGE CODE<br>16236 |   | DWG NO.<br>V62/12620 |  |

|-----------------------------------------|-----------|--------------------|---|----------------------|--|

|                                         |           | REV                | В | PAGE 12              |  |

TABLE I. Electrical performance characteristics - Continued. 1/

| Test                                                      | Symbol                | Conditions                      | Vcc       | Limits |     | Unit |

|-----------------------------------------------------------|-----------------------|---------------------------------|-----------|--------|-----|------|

|                                                           |                       | 2/                              |           | Min    | Max |      |

| Spy-Bi-Wire interface                                     |                       |                                 |           | •      |     | •    |

| Spy-Bi-Wire input frequency                               | f <sub>SBW</sub>      |                                 | 2.2 V/3 V | 0      | 20  | MHz  |

| Spy-Bi-Wire low clock pulse length                        | tsbw,Low              |                                 | 2.2 V/3 V | 0.025  | 15  | μs   |

| Spy-Bi-Wireenable time                                    | t <sub>SBW,En</sub>   | T <sub>A</sub> = -40°C to 105°C | 2.2 V/3 V |        | 1   | μs   |

| (Test high to acceptance of first clock edge <u>32</u> /) |                       |                                 |           |        |     |      |

| Spy-Bi-Wire return to normal operation time               | t <sub>SBW,Ret</sub>  |                                 | 2.2 V/3 V | 15     | 100 | μs   |

| Internal pulldown resistance on TEST                      | R <sub>Internal</sub> | T <sub>A</sub> = -40°C to 105°C | 2.2 V/3 V | 25     | 90  | kΩ   |

| JTAG fuse <u>33</u> / <u>37</u> /                         |                       |                                 |           |        |     | _    |

| Supply voltage during fuse blow condition                 | V <sub>CC(FB)</sub>   |                                 |           | 2.5    |     | V    |

| Voltage level on TEST for fuse blow                       | V <sub>FB</sub>       |                                 |           | 6      | 7   | V    |

| Supply current into TEST during fuse blow                 | I <sub>FB</sub>       |                                 |           |        | 100 | mA   |

| Time to blow fuse                                         | t <sub>FB</sub>       |                                 |           |        | 1   | ms   |

- <u>1</u>/ Testing and other quality control techniques are used to the extent deemed necessary to assure product performance over the specified temperature range. Product may not necessarily be tested across the full temperature range and all parameters may not necessarily be tested. In the absence of specific parametric testing, product performance is assured by characterization and/or design.

- Over recommended operating free air temperature range (unless otherwise noted). All inputs are tied to 0 V or to V<sub>CC</sub>. <u>2</u>/ Outputs do not source or sink any current.

- Current for brownout and WDT clocked by SMCLK included.

- 3/ 4/ 5/ 6/ Current for brownout and WDT clocked by ACLK included.

- Current for brownout included.

- The leakage current is measured with V<sub>SS</sub> or V<sub>CC</sub> applied to the corresponding pin(s), unless otherwise noted.

- <u>7</u>/ The leakage of the digital port pins is measured individually. The port pin is selected for input and the pullup/pulldown resistor is disabled.

- 8/ The maximum total current, I<sub>(OLmax)</sub> and I<sub>(OLmax)</sub>, for all outputs combined should not exceed ±48 mA to hold the maximum voltage drop specified.

- 9/ A resistive divider with two  $0.5 \text{ k}\Omega$  resistors between  $V_{CC}$  and  $V_{SS}$  is used as load. The output is connected to the center tap of

- The output voltage reaches at least 10% and 90% Vcc at the specified toggle frequency. <u>10</u>/

- 11/ The current consumption of the brownout module is already included in the ICC current consumption data. The voltage level  $V_{hys(B_IT-)}$  is  $\leq 1.8 \text{ V}$ .

- The DCO clock wake up time is measured from the edge of an external wake up signal (for example, port interrupt) to the first 12/ clock edge observable externally on a clock pin (MCLK or SMCLK).

- Parameter applicable only if DCOCLK is used for MCLK. <u>13</u>/

- 14/ Calculated using the box method:  $(MAX(-40^{\circ}C \text{ to } 85^{\circ}C) - MIN(-40^{\circ}C \text{ to } 85^{\circ}C)) / MIN(-40^{\circ}C \text{ to } 85^{\circ}C) / (85^{\circ}C - (-40^{\circ}C))$ .

- Calculated using the box method: (MAX(1.8 to 3.6 V) MIN(1.8 to 3.6 V)) / Min(1.8 to 3.6 V) / (3.6 V 1.8 V).

- The leakage current is defined in the leakage current table with Px.y/Ax parameter.

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO | SIZE<br>A | CAGE CODE<br>16236 |   | DWG NO.<br>V62/12620 |

|-----------------------------------------|-----------|--------------------|---|----------------------|

|                                         |           | REV                | В | PAGE 13              |

- 17/ The analog input voltage range must be within the selected reference voltage range V<sub>R+</sub> to V<sub>R-</sub> for valid conversion result.

- 18/ The internal reference supply current is not included in current consumption parameter IADC10.

- 19/ The internal reference current is supplied by terminal VCC. Consumption is independent of the ADC10ON control bit, unless a conversion is active. The REFON bit enables the built-in reference to settle before starting an A/D conversion.

- 20/ The external reference is used during conversion to charge and discharge the capacitance array. The input capacitance, C<sub>I</sub>, is also the dynamic load for an external reference during conversion. The dynamic impedance of the reference supply should follow the recommendations on analog source impedance to allow the charge to settle for 10 bit accuracy.

- 21/ The accuracy limits the minimum positive external reference voltage. Lower reference voltage levels may be applied with reduced accuracy requirements.

- 22/ Under this condition the external reference is internally buffered. The reference buffer is active and requires the reference buffer supply current IREFB. The current consumption can be limited to the sample and conversion period with REBURST = 1.

- 23/ The accuracy limits the maximum negative external reference voltage. Higher reference voltage levels may be applied with reduced accuracy requirements.

- <u>24</u>/ The accuracy limits the minimum external differential reference voltage. Lower differential reference voltage levels may be applied with reduced accuracy requirements.

- 25/ The condition is that the error in a conversion started after tadc100N is less than ±0.5 LSB. The reference and input signal are already settled.

- 26/ The sensor current I<sub>SENSOR</sub> is consuimed if (ADC10ON = 1 and REFON = 1) or (ADC10ON = 1 and INCH = 0Ah and sample signal is high). When REFON = 1, I<sub>SENSOR</sub> is included in IREF+. When REFON = 0, I<sub>SENSOR</sub> applies during conversion of the temperature sensor input (INCH = 0Ah).

- <u>27/</u> The following formula can be used to calculate the temperature sensor output voltage:

- $V_{Sensor, typ} = TC_{Sensor} (273 + T[^{\circ}C] + V_{Offset,sensor}[mV] \text{ or}$

- $V_{Sensor, typ} = TC_{Sensor} T[^{\circ}C] + V_{Sensor}(T_A = 0^{\circ}C)[mV].$

- $\frac{28}{20}$  The typical equivalent is impedance of the sensor is 51 k $\Omega$ . The sample time required includes the sensor-on time t<sub>SENSOR(on)</sub>.

- $\underline{29}$ / No additional current is needed. The  $V_{\text{MID}}$  is used during sampling.

- $\underline{30}$ / The on time  $t_{VMID(on)}$  is included in the sampling time  $t_{VMID(sample)}$ ; no additional on time is needed.

- 31/ This parameter defines the minimum supply voltage V<sub>CC</sub> when the data in RAM remains unchanged. No program execution should happen during this supply voltage condition.

- 32/ Tools accessing the Spy-Bi-Wire interface need to wait for the maximum t<sub>SBW,En</sub> time after pulling the TEST/SBWCLK pin high before applying the first SBWCLK clock edge.

- 33/ Once the fuse is blown, no further access to the JATG/Test, Spy-Bi-Wire, and emulation feature is possible, and JTAG is switched to bypass mode.

- 34/ Minimum and maximum parameters are characterized up to T<sub>A</sub> = 105°C unless otherwise noted.

- 35/ Over recommended operating free air temperature range unless otherwise noted.

- 36/ Over recommended ranges of supply voltage and up to operating free air temperature  $T_A = 105^{\circ}$ C (unless otherwise noted).

- 37/  $T_A = 25^{\circ}C$ , over recommended ranges of supply voltage (unless otherwise noted).

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO | SIZE<br>A | CAGE CODE<br>16236 |   | DWG NO.<br>V62/12620 |  |

|-----------------------------------------|-----------|--------------------|---|----------------------|--|

|                                         |           | REV                | В | PAGE 14              |  |

|        | Dimensions |      |        |       |        |              |      |        |       |  |

|--------|------------|------|--------|-------|--------|--------------|------|--------|-------|--|

| Symbol | Inch       | es   | Millim | eters | Symbol | Inch         | es   | Millim | eters |  |

|        | Min        | Max  | Min    | Max   |        | Min          | Max  | Min    | Max   |  |

| Α      |            | .069 |        | 1.75  | Е      | .150         | .157 | 3.80   | 4.00  |  |

| A1     | .004       | .010 | 0.10   | 0.25  | E1     | .228         | .244 | 5.80   | 6.20  |  |

| b      | .012       | .020 | 0.31   | 0.51  | е      | .050         | BSC  | 1.27   | BSC   |  |

| С      | .005       | .010 | 0.13   | 0.25  | L      | .016         | .050 | 0.40   | 1.27  |  |

| D      | .189       | .197 | 4.80   | 5.00  |        | <del>-</del> |      |        |       |  |

# NOTES:

- 1. All linear dimensions are in inches (millimeters).

- 2. This drawing is subject to change without notice.

- 3. Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 (0.15) each side.

- 4. Body width does not include interlead flash. Interlead flash shall not exceed .017 (0.43) each side.

- 5. Reference JEDEC MS-012.

FIGURE 1. Case outline.

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO | SIZE<br>A | CAGE CODE<br>16236 |   | DWG NO.<br>V62/12620 |

|-----------------------------------------|-----------|--------------------|---|----------------------|

|                                         |           | REV                | В | PAGE 15              |

| Terminal number | Terminal symbol       | Terminal number | Terminal symbol |

|-----------------|-----------------------|-----------------|-----------------|

| 1               | DVCC                  | 5               | DVSS            |

| 2               | P1.2/TA0.1/A2         | 6               | TEST/SBWTCK     |

| 3               | P1.5/TA0.0/A5/SCLK    | 7               | RST/NMI/SBWTDIO |

| 4               | P1.6/TA0.1/A6/SDO/SCL | 8               | P1.7/A7/SDI/SDA |

FIGURE 2. <u>Terminal connections</u>.

| Term    | Term inal I/O |     | Description                                                                                |

|---------|---------------|-----|--------------------------------------------------------------------------------------------|

| Name    | No.           |     |                                                                                            |

| P1.2/   | 2             | I/O | General purpose digital I/O pin                                                            |

| TA0.1/  |               |     | Timer_A, capture: CCI1A input, compare Out1 output                                         |

| A2      |               |     | ADC10 analog input A2                                                                      |

| P1.5/   | 3             | I/O | General purpose digital I/O pin                                                            |

| TA0.0/  |               |     | Timer_A, compare Out0 output                                                               |

| A5/     |               |     | ADC10 analog input A5                                                                      |

| SCLK    |               |     | USI: clock input in I2C mode; clock input/output in SPI mode                               |

| P1.6/   | 4             | I/O | General purpose digital I/O pin                                                            |

| TA0.1/  |               |     | Timer_A, capture: CCI1B input, compare Out1 output                                         |

| A6/     |               |     | ADC10 analog input A6                                                                      |

| SDO/    |               |     | USI: Data output in SPI mode                                                               |

| SCL     |               |     | USI: I2C clock in I2C mode                                                                 |

| P1.7/   | 5             | I/O | General purpose digital I/O pin                                                            |

| A7/     |               |     | ADC10 analog input A7                                                                      |

| SDI/    |               |     | USI: Data output in SPI mode                                                               |

| SDA     |               |     | USI: Data input in I2C mode                                                                |

| RST/    | 6             | I   | Reset imput                                                                                |

| NMI/    |               |     | Nonmaskable interrupt input                                                                |

| SBWTDIO |               |     | Spy-Bi-Wire test data input/output during programming and test                             |

| TEST/   | 7             | I   | Select test mode for JTAG pins on Port 1. The device protection fuse is connected to TEST. |

| SBWTCK  |               |     | Spy-Bi-Wire test clock input during programming and test.                                  |

| DVCC    | 1             |     | Digital supply voltage                                                                     |

| DVSS    | 8             |     | Digital ground reference                                                                   |

The GPIOs P1.0, P1.1, P1.3, P1.4, P2.6, and P2.7 are implemented but not available on the device pinout. To avoid floating inputs, these digital I/Os should be properly configured. The pullup or pulldown resistors of the unbounded P1.x GPIOs should be enabled, and the VLO should be selected as the ACLK source. (See manufacturer for more information).

FIGURE 3. Terminal function.

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO | SIZE<br>A | CAGE CODE<br>16236 |   | DWG NO.<br>V62/12620 |

|-----------------------------------------|-----------|--------------------|---|----------------------|

|                                         |           | REV                | В | PAGE 16              |

FIGURE 4. Functional block diagram.

| DLA LAND AND MARITIME | SIZE<br>A | CAGE C<br>1623 | _ | DWG NO.<br>V62/12620 |

|-----------------------|-----------|----------------|---|----------------------|

| COLUMBUS, OHIO        |           | REV            | В | PAGE 17              |

# NOTE:

1. Minimum processor frequency is defined by system clock. Flash program or erase operations require a minimum  $V_{CC}$  of 2.2 V.

FIGURE 5. Safe operating area.

FIGURE 6. POR/Brownout Reset (BOR) vs Supply voltage.

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO | SIZE<br>A | CAGE CODE<br>16236 |   | DWG NO.<br>V62/12620 |

|-----------------------------------------|-----------|--------------------|---|----------------------|

|                                         |           | REV                | В | PAGE 18              |

FIGURE 7. VCC(drop) level with a Square voltage drop to generate a POR/Brownout signal.

$\label{eq:conditional} \text{FIGURE 8.} \ \ \underline{\text{V}_{\text{CC(drop)}} \text{level with a Triangle voltage drop to generate a POR/Brownout signal}}.$

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO | SIZE<br>A | CAGE CODE<br>16236 |   | DWG NO.<br>V62/12620 |

|-----------------------------------------|-----------|--------------------|---|----------------------|

|                                         |           | REV                | В | PAGE 19              |

FIGURE 9. DCO wake-up time from LPM3/4 vs DCO frequency.

FIGURE 10. <u>USI low level output voltage vs output current</u>.

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO | SIZE<br>A | CAGE CODE<br>16236 |   | DWG NO.<br>V62/12620 |

|-----------------------------------------|-----------|--------------------|---|----------------------|

|                                         |           | REV                | В | PAGE 20              |

#### 4. VERIFICATION

4.1 <u>Product assurance requirements</u>. The manufacturer is responsible for performing all inspection and test requirements as indicated in their internal documentation. Such procedures should include proper handling of electrostatic sensitive devices, classification, packaging, and labeling of moisture sensitive devices, as applicable.

#### 5. PREPARATION FOR DELIVERY

- 5.1 <u>Packaging</u>. Preservation, packaging, labeling, and marking shall be in accordance with the manufacturer's standard commercial practices for electrostatic discharge sensitive devices.

- 6. NOTES

- 6.1 ESDS. Devices are electrostatic discharge sensitive and are classified as ESDS class 1 minimum.

- 6.2 <u>Configuration control</u>. The data contained herein is based on the salient characteristics of the device manufacturer's data book. The device manufacturer reserves the right to make changes without notice. This drawing will be modified as changes are provided.

- 6.3 <u>Suggested source(s) of supply</u>. Identification of the suggested source(s) of supply herein is not to be construed as a guarantee of present or continued availability as a source of supply for the item. DLA Land and Maritime maintains an online database of all current sources of supply at <a href="https://landandmaritimeapps.dla.mil/programs/smcr/">https://landandmaritimeapps.dla.mil/programs/smcr/</a>.

| Vendor item drawing administrative control number <u>1</u> / | Device<br>manufacturer<br>CAGE code | Top side<br>marking | Transport<br>media | Vendor part number |

|--------------------------------------------------------------|-------------------------------------|---------------------|--------------------|--------------------|

| V62/12620-01XE                                               | 01295                               | G230EP              | Tape and real      | MSP430G2230QDREP   |

|                                                              |                                     |                     | Tube               | MSP430G2230QREP    |

1/ The vendor item drawing establishes an administrative control number for identifying the item on the engineering documentation.

CAGE code

01295

Source of supply

Texas Instruments, Inc. Semiconductor Group 8505 Forest Lane P.O. Box 660199 Dallas, TX 75243

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO | SIZE<br>A | CAGE CODE<br>16236 |   | DWG NO.<br>V62/12620 |

|-----------------------------------------|-----------|--------------------|---|----------------------|

|                                         |           | REV                | В | PAGE 21              |