| 1   | REVISIONS                                                                                                                   |          |                |  |  |  |  |  |  |

|-----|-----------------------------------------------------------------------------------------------------------------------------|----------|----------------|--|--|--|--|--|--|

| LTR | DESCRIPTION                                                                                                                 | DATE     | APPROVED       |  |  |  |  |  |  |

| Α   | Add top side marking in section 6.3phn                                                                                      | 13-03-21 | Thomas M. Hess |  |  |  |  |  |  |

| В   | Correct part number in section 6.3 phn                                                                                      | 14-05-05 | Thomas M. Hess |  |  |  |  |  |  |

| С   | Corret the operating temperature range in Section 1.1 and 1.4. Update boilerplate to current MIL-PRF-38535 requirements PHN | 19-02-05 | Thomas M. Hess |  |  |  |  |  |  |

Prepared in accordance with ASME Y14.24

REV PAGE Vendor item drawing

| REV                                  |     |                           |                            |                          |   |   |                                                                                    |                   |                                                                                                        |     |            |    |    |    |    |  |  |  |

|--------------------------------------|-----|---------------------------|----------------------------|--------------------------|---|---|------------------------------------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------|-----|------------|----|----|----|----|--|--|--|

| PAGE                                 |     |                           |                            |                          |   |   |                                                                                    |                   |                                                                                                        |     |            |    |    |    |    |  |  |  |

| REV STATUS                           | RE\ | /                         | •                          | С                        | С | С | С                                                                                  | С                 | С                                                                                                      | С   | С          | С  | С  | С  | С  |  |  |  |

| OF PAGES                             | PAC | 3E                        |                            | 1                        | 2 | 3 | 4                                                                                  | 5                 | 6                                                                                                      | 7   | 8          | 9  | 10 | 11 | 12 |  |  |  |

| PMIC N/A                             |     | PREPARED BY Phu H. Nguyen |                            |                          |   |   | DLA LAND AND MARITIME COLUMBUS, OHIO 43218-3990 http://www.dla.mil/landandmaritime |                   |                                                                                                        |     |            |    |    |    |    |  |  |  |

| Original date of drawing<br>YY MM DD |     | CHE                       | CHECKED BY Phu H. Nguyen   |                          |   |   |                                                                                    | TITLE             |                                                                                                        |     |            |    |    |    |    |  |  |  |

| 12-04-24                             |     | APP                       | APPROVED BY Thomas M. Hess |                          |   |   |                                                                                    |                   | MICROCIRCUIT, DIGITAL, 200 MHz GENERAL<br>PURPOSE CLOCK BUFFER, PCI-X COMPLIANT,<br>MONOLITHIC SILICON |     |            |    |    |    |    |  |  |  |

|                                      |     |                           | ZE<br><b>A</b>             | CODE IDENT. NO.<br>16236 |   |   |                                                                                    | DWG NO. V62/12618 |                                                                                                        |     |            |    |    |    |    |  |  |  |

|                                      |     | REV                       | '                          |                          |   | С |                                                                                    |                   |                                                                                                        | PAG | <b>E</b> 1 | OF | 12 |    |    |  |  |  |

## 1. SCOPE

- 1.1 <u>Scope</u>. This drawing documents the general requirements of a high performance 200 MHz general purpose clock buffer, PCI-X compliant microcircuit, with an operating temperature range of -40°C to +105°C.

- 1.2 <u>Vendor Item Drawing Administrative Control Number</u>. The manufacturer's PIN is the item of identification. The vendor item drawing establishes an administrative control number for identifying the item on the engineering documentation:

V62/12618

01

X

E

Drawing number

Device type (See 1.2.1)

Case outline (See 1.2.2)

Lead finish (See 1.2.3)

1.2.1 Device type(s).

Device type

Generic

Circuit function

01

CDCV304-EP

200 MHz general purpose clock buffer, PCI-X compliant

1.2.2 <u>Case outline(s)</u>. The case outlines are as specified herein.

Outline letter

Number of pins

JEDEC PUB 95

Package style

X

8

JEDEC MO-153

Plastic small outline

1.2.3 <u>Lead finishes</u>. The lead finishes are as specified below or other lead finishes as provided by the device manufacturer:

Finish designator <u>Material</u> Α Hot solder dip В Tin-lead plate Gold plate С D Palladium Ε Gold flash palladium F Tin-lead alloy Ζ Other

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |  |  |

|-----------------------|------|----------------|------------------|--|--|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/12618</b> |  |  |

|                       |      | REV C          | PAGE 2           |  |  |

## 1.3 Absolute maximum ratings. 1/

| Supply voltage range, (V <sub>DD</sub> )                                                    | 0.5 V to 4.3 V                         |

|---------------------------------------------------------------------------------------------|----------------------------------------|

| Input voltage range, (V <sub>I</sub> )                                                      | 0.5 V to V <sub>DD</sub> + 0.5 V 2/ 3/ |

| Output voltage range, (Vo)                                                                  |                                        |

| Input clamp current, (IIK) (VI < 0 or VI > VDD)                                             |                                        |

| Output clamp current, (lok) (Vo < 0 or Vo >VDD)                                             |                                        |

| Continuous total output current, (I <sub>O</sub> ) (V <sub>O</sub> = 0 to V <sub>DD</sub> ) |                                        |

| Storage temperature range (Tstg)                                                            |                                        |

## Thermal information 4/

| Case X                                                                        |       | Unit |

|-------------------------------------------------------------------------------|-------|------|

| Junction to ambient thermal resistance ( $\theta_{JA}$ ) $5/$                 | 157.8 | °C/W |

| Junction to case (top) thermal resistance ( $\theta_{JA}$ ) $\underline{6}$ / | 61.8  |      |

| Junction to board thermal resistance $(\theta_{JA})$ $7/$                     | 104.3 |      |

| Junction to top characterization parameter $(\Psi_{JT})$ 8/                   | 7.7   |      |

| Junction to board characterization parameter ( $\Psi_{JB}$ ) <u>9</u> /       | 102.6 |      |

## 1.4 Recommended operating conditions.

| Supply voltage, (V <sub>DD</sub> )                | . 2.3 V to 3.6 V                  |

|---------------------------------------------------|-----------------------------------|

| Low level input voltage, (V <sub>IL</sub> )       | . 0.3 x V <sub>DD</sub> V maximum |

| High level input voltage, (V <sub>IH</sub> )      | . 0.7 x V <sub>DD</sub> V minimum |

| High level output current, (I <sub>OH</sub> ):    |                                   |

| V <sub>DD</sub> = 2.5 V                           | 12 mA maximum                     |

| $V_{DD} = 3.3 \text{ V}$                          | 24 mA maximum                     |

| Low level output current, (IoL):                  |                                   |

| $V_{DD} = 2.5 \text{ V}$                          | . 12 mA maximum                   |

| V <sub>DD</sub> = 3.3 V                           | . 24 mA maximum                   |

| Operating free air temperature, (T <sub>A</sub> ) | 40°C to 105°C                     |

| Clock frequency (fclk)                            |                                   |

|                                                   |                                   |

Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

| DLA LAND AND MARITIME | SIZE     | CODE IDENT NO. | DWG NO.          |  |  |

|-----------------------|----------|----------------|------------------|--|--|

| COLUMBUS, OHIO        | <b>A</b> | <b>16236</b>   | <b>V62/12618</b> |  |  |

|                       |          | REV C          | PAGE 3           |  |  |

<sup>2/</sup> The input and output negative voltage ratings may be exceeded if the input and output clamp current ratings are observed.

<sup>3/</sup> This value is limited to 4.6 V maximum.

<sup>4/</sup> For more information about tradition and new thermal metrics, see manufacturer data.

<sup>5/</sup> The junction to ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC standard, high K board, as specified in JESD51-7, in an environment described in JESD51-2a.

<sup>6/</sup> The junction to case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDEC standard exists, but a close description can be found in the ANSI SEMI standard G30-88.

<sup>7/</sup> The junction to board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

<sup>8/</sup> The Junction to top characterization parameter , Ψ<sub>JT</sub>, estimates the junction temperature of a device in a real system and in extracted from the simulation data for obtaining θ<sub>JA</sub>, using a procedure described in JESD51-2a.

<sup>9/</sup> The Junction to board characterization parameter , Ψ<sub>JB</sub>, estimates the junction temperature of a device in a real system and in extracted from the simulation data for obtaining θ<sub>JA</sub>, using a procedure described in JESD51-2a

## 2. APPLICABLE DOCUMENTS

## JEDEC - SOLID STATE TECHNOLOGY ASSOCIATION (JEDEC)

JEP95 - Registered and Standard Outlines for Semiconductor Devices

JESD51-2 - Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air)

JESD51-7 - High Effective Thermal Conductivity Test Board for Leaded Surface Mount Packages

JESD51-8 – Junction-to-board thermal resistance Theta-JB or RθJB.

Applications for copies should be addressed to the Electronic Industries Alliance, 3103 North 10th Street, Suite 240–S, Arlington, VA 22201-2107 or online at <a href="https://www.jedec.org">https://www.jedec.org</a>.

#### 3. REQUIREMENTS

- 3.1 <u>Marking</u>. Parts shall be permanently and legibly marked with the manufacturer's part number as shown in 6.3 herein and as follows:

- A. Manufacturer's name, CAGE code, or logo

- B. Pin 1 identifier

- C. ESDS identification (optional)

- 3.2 <u>Unit container</u>. The unit container shall be marked with the manufacturer's part number and with items A and C (if applicable) above.

- 3.3 <u>Electrical characteristics</u>. The maximum and recommended operating conditions and electrical performance characteristics are as specified in 1.3, 1.4, and table I herein.

- 3.4 <u>Design, construction, and physical dimension</u>. The design, construction, and physical dimensions are as specified herein.

- 3.5 Diagrams.

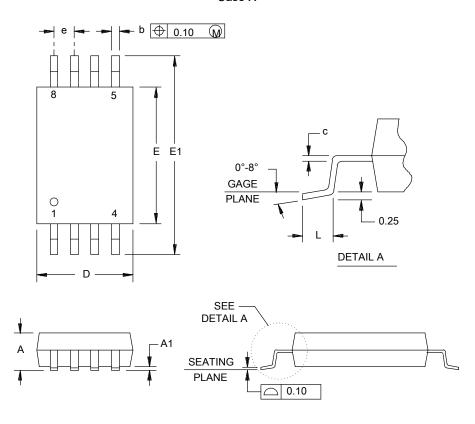

- 3.5.1 <u>Case outline</u>. The case outline shall be as shown in 1.2.2 and figure 1.

- 3.5.2 <u>Terminal connections</u>. The terminal connections shall be as shown in figure 2.

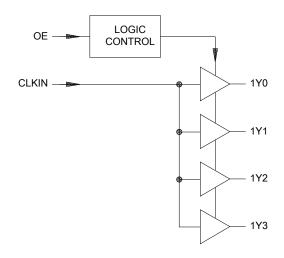

- 3.5.3 <u>Functional block diagram</u>. The functional block diagram shall be as shown in figure 3.

- 3.5.4 <u>Terminal function</u>. The terminal function shall be as shown in figure 4.

- 3.5.5 <u>Test load circuit</u>. The test load circuit shall be as shown in figure 5.

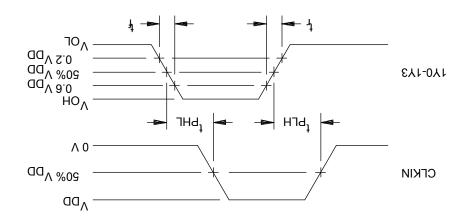

- 3.5.6 <u>Voltage waveforms propagation delay (t<sub>pd</sub>) measurements</u>. The Voltage waveforms propagation delay (t<sub>pd</sub>) measurements shall be as shown in figure 6.

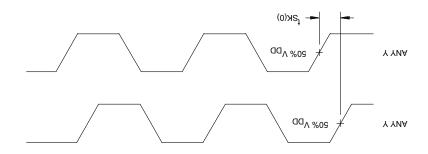

- 3.5.7 <u>Output skew</u>. The output skew shall be as shown in figure 7.

- 3.5.8 Clock waveform. The clock waveform shall be as shown in figure 8.

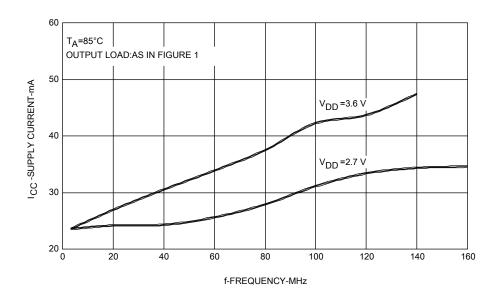

- 3.5.9 Supply current vs frequency. The supply current vs frequency shall be as shown in figure 9.

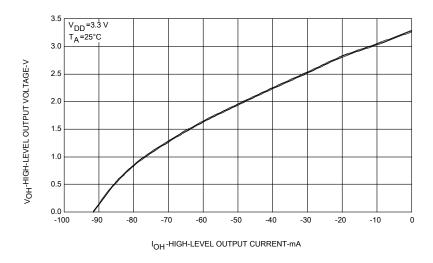

- 3.5.10 <u>High level output voltage vs high level output current</u>. The high level output voltage vs high level output current shall be as shown in figure 10.

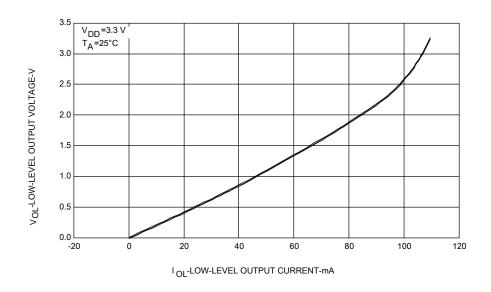

- 3.5.11 <u>Low level output voltage vs low level output current</u>. The low level output voltage vs low level output current shall be as shown in figure 11.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |  |  |

|-----------------------|------|----------------|------------------|--|--|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/12618</b> |  |  |

|                       |      | REV C          | PAGE 4           |  |  |

TABLE I. <u>Electrical performance characteristics</u>. <u>1</u>/

| Test                           | Symbol          | Conditions                                             | Limi         | Limits |    |  |

|--------------------------------|-----------------|--------------------------------------------------------|--------------|--------|----|--|

|                                |                 | <u>2</u> /                                             | Min          | Max    |    |  |

| Input voltage                  | Vık             | V <sub>DD</sub> = 3 V, I <sub>I</sub> = -18 mA         |              | -1.2   | V  |  |

|                                |                 | $V_{DD} = 2.3 \text{ V}, I_{OH} = -8 \text{ mA}$       | 1.78         |        | V  |  |

|                                |                 | $V_{DD}$ = min to max, $I_{OH}$ = -1 mA                | $V_{DD}-0.3$ |        |    |  |

| High level output voltage      | Vон             | $V_{DD} = 3 \text{ V}, I_{OH} = -24 \text{ mA}$        | 1.9          |        |    |  |

|                                |                 | V <sub>DD</sub> = 3 V, I <sub>OH</sub> = -12 mA        | 2.3          |        |    |  |

|                                |                 | $V_{DD} = 2.3 \text{ V}, I_{OL} = 8 \text{ mA}$        |              | 0.51   | V  |  |

|                                |                 | $V_{DD}$ = min to max, $I_{OL}$ = 1 mA                 |              | 0.2    |    |  |

| Low level output voltage       | V <sub>OH</sub> | $V_{DD} = 3 \text{ V}, I_{OL} = 24 \text{ mA}$         |              | 0.84   |    |  |

|                                |                 | $V_{DD} = 3 \text{ V}, I_{OL} = 12 \text{ mA}$         |              | 0.60   |    |  |

| High level output current      | I <sub>OH</sub> | V <sub>DD</sub> = 3 V, V <sub>O</sub> = 1 V            | -45          |        | mA |  |

| g                              | -011            | $V_{DD} = 3.3 \text{ V}, V_{O} = 1.65 \text{ V}$       | -55 T        | ΥP     |    |  |

| Low level output current       | lou             | $V_{DD} = 3 \text{ V}, \ V_{O} = 2 \text{ V}$          | 54           |        |    |  |

| 25W 15V61 Sulput Sull ont      | IOL             | $V_{DD} = 3.3 \text{ V}, V_{O} = 1.65 \text{ V}$       | 70 T         | /P     |    |  |

| Input current                  | l <sub>l</sub>  | V <sub>I</sub> = V <sub>O</sub> or V <sub>DD</sub>     |              | ±5     | μA |  |

| Dynamic current, See Figure 9. | Ipp             | f = 67 MHz, V <sub>DD</sub> = 2.7 V                    |              | 28     | mA |  |

| Zynamie sament, 300 i igulo o. | טטי             | f = 67 MHz, V <sub>DD</sub> = 3.6 V                    |              | 37     |    |  |

| Input capacitance              | Cı              | $V_{DD} = 3.3 \text{ V}, V_O = 0 \text{ V or } V_{DD}$ | 3 TYP        |        | pF |  |

| Output capacitance             | Co              | $V_{DD} = 3.3 \text{ V}, V_O = 0 \text{ V or } V_{DD}$ | 3.2 T        | ΥP     |    |  |

See footnote at end of table.

| DLA LAND AND MARITIME | SIZE     | CODE IDENT NO. | DWG NO.          |  |  |

|-----------------------|----------|----------------|------------------|--|--|

| COLUMBUS, OHIO        | <b>A</b> | <b>16236</b>   | <b>V62/12618</b> |  |  |

|                       |          | REV C          | PAGE 5           |  |  |

TABLE I. <u>Electrical performance characteristics</u> – Continued. <u>1</u>/

| Test                                                    | Symbol                      | Conditions                                    | Lim            | Unit |        |  |

|---------------------------------------------------------|-----------------------------|-----------------------------------------------|----------------|------|--------|--|

|                                                         | <u>2</u> /                  |                                               | Min Max        |      |        |  |

| Switching characteristics for $V_{DD}$ = 2.5 V ±10      | 0%, C <sub>L</sub> = 10 pF  | (unless otherwise noted)                      |                |      |        |  |

| Low to high propagation delay                           | t <sub>PLH</sub>            | See figure                                    | 2              | 4.5  | ns     |  |

| High to low propagation delay                           | t <sub>PHL</sub>            |                                               | 2              | 4.5  |        |  |

| Output skew 3/                                          | $t_{sk(o)}$                 | See figure                                    |                | 150  | ps     |  |

| Output rise slew rate                                   | $t_r$                       |                                               | 1              | 4    | V/ns   |  |

| Output fall slew rate                                   | $t_f$                       |                                               | 1              | 4    |        |  |

| Switching characteristics for V <sub>DD</sub> = 3.3±10% | , C <sub>L</sub> = 10 pF (ι | ınless otherwise noted)                       | _ <del>!</del> |      |        |  |

| Low to high propagation delay                           | t <sub>PLH</sub>            | See figure                                    | 1.8            | 3.8  | ns     |  |

| High to low propagation delay                           | t <sub>PHL</sub>            |                                               | 1.8            | 3.8  |        |  |

| Output skew <u>3</u> /                                  | t <sub>sk(o)</sub>          | See figure                                    |                | 100  | ps     |  |

| Additive phase jitter from input to output 1Y0          | t <sub>jitter</sub>         | 12 kHz to 5 MHz, f <sub>out</sub> = 30.72 MHz | 63 TYP         |      | fs rms |  |

|                                                         |                             | 12 kHz to 20 MHz, f <sub>out</sub> = 125 MHz  | 56 TYP         |      |        |  |

| Pulse skew                                              | t <sub>sk(p)</sub>          |                                               | 180            | TYP  | ps     |  |

| Process skew                                            | t <sub>sk(pr)</sub>         |                                               | 0.2            | ГҮР  | ns     |  |

| Part to part skew                                       | t <sub>sk(pp)</sub>         |                                               | 0.25           | TYP  |        |  |

| Clock high time,                                        | thigh                       | 66 MHz                                        | 6              |      |        |  |

| See figure 8.                                           |                             | 140 MHz                                       | 2.2            |      |        |  |

| Clock low time,                                         | t <sub>low</sub>            | 66 MHz                                        | 6              |      |        |  |

| See figure 8.                                           |                             | 140 MHz                                       | 3              |      |        |  |

| Output rise slew rate 4/                                | t <sub>r</sub>              | V <sub>O</sub> = 0.4 V to 2 V                 | 1.5 4          |      | V/ns   |  |

| Output rise fall rate 4/                                | t <sub>f</sub>              | V <sub>O</sub> = 2 V to 0.4 V                 | 1.5            | 4    | 1      |  |

<sup>&</sup>lt;u>1</u>/ Testing and other quality control techniques are used to the extent deemed necessary to assure product performance over the specified temperature range. Product may not necessarily be tested across the full temperature range and all parameters may not necessarily be tested. In the absence of specific parametric testing, product performance is assured by characterization and/or

| DLA LAND AND MARITIME | SIZE     | CODE IDENT NO. | DWG NO.          |

|-----------------------|----------|----------------|------------------|

| COLUMBUS, OHIO        | <b>A</b> | <b>16236</b>   | <b>V62/12618</b> |

|                       |          | REV C          | PAGE 6           |

<sup>&</sup>lt;u>2</u>/ Over recommended operating free air temperature range (unless otherwise noted). All typical values are with respect to nominal V<sub>DD</sub> and  $T_A = 25$ °C.

The  $t_{sk(o)}$  specification is only valid for equal loading of all outputs and  $T_A = -40$ °C to 85°C

<sup>&</sup>lt;u>3/</u> This symbol is according to PCI-X terminology.

| Dimensions |             |      |        |             |      |  |

|------------|-------------|------|--------|-------------|------|--|

| Symbol     | Millimeters |      | Symbol | Millimeters |      |  |

|            | Min         | Max  |        | Min         | Max  |  |

| Α          |             | 1.20 | Е      | 4.30        | 4.50 |  |

| A1         | 0.05        | 0.15 | E1     | 6.20        | 6.60 |  |

| b          | 0.19        | 0.30 | е      | 0.65 BSC    |      |  |

| С          | 0.15        | NOM  | L      | 0.50 0.75   |      |  |

| D          | 2.90        | 3.10 |        |             |      |  |

# NOTES:

- 1. All linear dimensions are in millimeters.

- 2. This drawing is subject to change without notice.

- Body dimensions do not include mold flash, protrusions, or gate burrs. Mold flash, protrusion, or gate burrs shall not exceed 0.15 each side.

- Body width does not include interlead flash. Interlead flash shall not exceed 0.25 each side Falls within JEDEC MO-153.

FIGURE 1. Case outline.

| DLA LAND AND MARITIME | SIZE     | CODE IDENT NO. | DWG NO.          |

|-----------------------|----------|----------------|------------------|

| COLUMBUS, OHIO        | <b>A</b> | <b>16236</b>   | <b>V62/12618</b> |

|                       |          | REV C          | PAGE 7           |

|                 | Case outline X  |                 |                 |  |  |  |

|-----------------|-----------------|-----------------|-----------------|--|--|--|

| Terminal number | Terminal symbol | Terminal number | Terminal symbol |  |  |  |

| 1               | CLKIN           | 5               | 1Y1             |  |  |  |

| 2               | OE              | 6               | VDD             |  |  |  |

| 3               | 1Y0             | 7               | 1Y2             |  |  |  |

| 4               | GND             | 8               | 1Y3             |  |  |  |

FIGURE 2. <u>Terminal connections</u>.

FIGURE 3. Functional block diagram.

| Ter      | minal      | I/O   | Description               |

|----------|------------|-------|---------------------------|

| Name     | No.        |       | Becompaign                |

| 1Y[0:3]  | 3, 5, 7, 8 | 0     | Buffered output clocks    |

| CLKIN    | 1          | Ι     | Input reference frequency |

| GND      | 4          | Power | Ground                    |

| OE       | 2          | I     | Output enable control     |

| $V_{DD}$ | 6          | Power | Supply                    |

FIGURE 4. <u>Terminal function</u>.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/12618</b> |

|                       |      | REV C          | PAGE 8           |

| SEΛ C                                   |                                        |  |

|-----------------------------------------|----------------------------------------|--|

| SIZE CODE IDEN  COLUMBUS, OHIO  A 16236 | DLA LAND AND MARITIMI<br>OIHO ,SUBMUJO |  |

FIGURE 7. Output skew

FIGURE 6. Voltage waveforms propagation delay (tod) measurements.

FIGURE 5. Test load circuit.

**ੂ0**⊅।

$aa_{\Lambda}$

|                                                                   |                                                                    |             | CYC -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------------------------|--------------------------------------------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PARAMETER                                                         | VALUE                                                              | UNIT        | HIGH - LOW - |

| V <sub>IH(MIN)</sub><br>V <sub>IL(MAX)</sub><br>V <sub>TEST</sub> | 0.5 V <sub>DD</sub><br>0.35 V <sub>DD</sub><br>0.4 V <sub>DD</sub> | V<br>V<br>V | VIH(MIN) VTEST VIL(MAX)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                   |                                                                    |             | 0.4 V <sub>DD</sub><br>PEAK TO PEAK<br>(MINIMUM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

# NOTE:

1. All parameters in this figure are according to PCI-X 1.0 specifications.

FIGURE 8. Clock waveform.

FIGURE 9. Supply current vs Frquency.

| DLA LAND AND MARITIME | SIZE     | CODE IDENT NO. | DWG NO.          |

|-----------------------|----------|----------------|------------------|

| COLUMBUS, OHIO        | <b>A</b> | <b>16236</b>   | <b>V62/12618</b> |

|                       |          | REV C          | PAGE 10          |

FIGURE 10. High level output voltage vs high level output current.

FIGURE 11. Low level output voltage vs low level output current.

| DLA LAND AND MARITIME | SIZE     | CODE IDENT NO. | DWG NO.          |

|-----------------------|----------|----------------|------------------|

| COLUMBUS, OHIO        | <b>A</b> | <b>16236</b>   | <b>V62/12618</b> |

|                       |          | REV C          | PAGE 11          |

## 4. VERIFICATION

4.1 <u>Product assurance requirements</u>. The manufacturer is responsible for performing all inspection and test requirements as indicated in their internal documentation. Such procedures should include proper handling of electrostatic sensitive devices, classification, packaging, and labeling of moisture sensitive devices, as applicable.

## 5. PREPARATION FOR DELIVERY

- 5.1 <u>Packaging</u>. Preservation, packaging, labeling, and marking shall be in accordance with the manufacturer's standard commercial practices for electrostatic discharge sensitive devices.

- 6. NOTES

- 6.1 ESDS. Devices are electrostatic discharge sensitive and are classified as ESDS class 1 minimum.

- 6.2 <u>Configuration control</u>. The data contained herein is based on the salient characteristics of the device manufacturer's data book. The device manufacturer reserves the right to make changes without notice. This drawing will be modified as changes are provided.

- 6.3 <u>Suggested source(s) of supply</u>. Identification of the suggested source(s) of supply herein is not to be construed as a guarantee of present or continued availability as a source of supply for the item. DLA Land and Maritime maintains an online database of all current sources of supply at <a href="https://landandmaritimeapps.dla.mil/programs/smcr/">https://landandmaritimeapps.dla.mil/programs/smcr/</a>.

| Vendor item drawing administrative control number 1/ CAGE code |       | Vendor part number | Top side marking |

|----------------------------------------------------------------|-------|--------------------|------------------|

| V62/12618-01XE                                                 | 01295 | CDCV304TPWREP      | CDCV304-EP       |

1/ The vendor item drawing establishes an administrative control number for identifying the item on the engineering documentation.

CAGE code

Source of supply

Texas Instruments, Inc.

Semiconductor Group

8505 Forest Lane

P.O. Box 660199

Dallas, TX 75243

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/12618</b> |

|                       |      | REV C          | PAGE 12          |