|     | REVISIONS                                                                 |                 |                   |

|-----|---------------------------------------------------------------------------|-----------------|-------------------|

| LTR | DESCRIPTION                                                               | DATE (YR-MO-DA) | APPROVED          |

| Α   | Update boilerplate paragraphs to current requirements PHN                 | 11-02-01        | David J. Corbett  |

| В   | Update boilerplate to current MIL-PRF-38535 requirements PHN              | 16-05-20        | Thomas M. Hess    |

| С   | Update boilerplate paragraphs to current VID description requirements DRH | 22-11-15        | Muhammad A. Akbar |

CURRENT DESIGN ACTIVITY CAGE CODE 16236 HAS CHANGED NAMES TO: DLA LAND AND MARITIME COLUMBUS, OHIO 43218-3990

Prepared in accordance with ASME Y14.24

Vendor Item Drawing

|                 |                           |   |   |   |   |   |   |   |  |  |  |  |  |  |  | <br> |

|-----------------|---------------------------|---|---|---|---|---|---|---|--|--|--|--|--|--|--|------|

| Revision Status | Revision Status of Sheets |   |   |   |   |   |   |   |  |  |  |  |  |  |  |      |

| REV             |                           |   |   |   |   |   |   |   |  |  |  |  |  |  |  |      |

| SHEET           |                           |   |   |   |   |   |   |   |  |  |  |  |  |  |  |      |

| REV             | С                         | С | С | С | С | С | С | С |  |  |  |  |  |  |  |      |

| SHEET           | 1                         | 2 | 3 | 4 | 5 | 6 | 7 | 8 |  |  |  |  |  |  |  |      |

| PMIC N/A         | PREPARE<br>Thanh V. I |           | DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990<br>https://www.dla.mil/landandmaritime |  |  |  |  |  |

|------------------|-----------------------|-----------|-------------------------------------------------------------------------------------------|--|--|--|--|--|

| Original date of | CHECKE                | ) BY      | TITLE                                                                                     |  |  |  |  |  |

| drawing          | Thanh V. I            | Nguyen    | MICROCIRCUIT, DIGITAL, HIGH SPEED CMOS, HEX INVERTER, TTL COMPATIBLE INPUTS,              |  |  |  |  |  |

|                  | APPROVE               | ED BY     | MONOLITHIC SILICON                                                                        |  |  |  |  |  |

|                  | Thomas M              | I. Hess   |                                                                                           |  |  |  |  |  |

| 04-04-13         | SIZE                  | CAGE CODE | DWG NO.                                                                                   |  |  |  |  |  |

|                  | Α                     | 16236     | V62/04697                                                                                 |  |  |  |  |  |

|                  | REV                   | С         | PAGE 1 OF 8                                                                               |  |  |  |  |  |

#### 1. SCOPE

- 1.1 <u>Scope</u>. This drawing documents the general requirements of a high performance hex inverter microcircuit, with an operating temperature range of -40°C to +85°C.

- 1.2 <u>Vendor Item Drawing Administrative Control Number</u>. The manufacturer's PIN is the item of identification. The vendor item drawing establishes an administrative control number for identifying the item on the engineering documentation:

| V62/04697      | - | <u>01</u><br>              | X<br>T                      | Ę                          |

|----------------|---|----------------------------|-----------------------------|----------------------------|

| Drawing number |   | Device type<br>(See 1.2.1) | Case outline<br>(See 1.2.2) | Lead finish<br>(See 1.2.3) |

1.2.1 Device type(s).

Device type

Generic

Circuit function

01

74HCT04-EP

Hex inverter, TTL compatible inputs

1.2.2 <u>Case outline(s)</u>. The case outlines are as specified herein.

| Outline letter | Number of pins | JEDEC PUB 95 | Package style                 |

|----------------|----------------|--------------|-------------------------------|

| X              | 14             | MS-012       | Plastic small-outline package |

1.2.3 Lead finishes. The lead finishes are as specified below or other lead finishes as provided by the device manufacturer:

| Finish designator | <u>Material</u>      |  |  |  |  |

|-------------------|----------------------|--|--|--|--|

| Α                 | Hot solder dip       |  |  |  |  |

| В                 | Tin-lead plate       |  |  |  |  |

| С                 | Gold plate           |  |  |  |  |

| D                 | Palladium            |  |  |  |  |

| E                 | Gold flash palladium |  |  |  |  |

1.3 Absolute maximum ratings. 1/

| Supply voltage range (V <sub>CC</sub> )                                              | 0.5 V to 7.0 V    |

|--------------------------------------------------------------------------------------|-------------------|

| Input clamp current $(I_{IK})$ $(V_I < 0 \text{ or } V_I > V_{CC})$                  | ±20 mA <u>2</u> / |

| Output clamp current (Iok) (Vo < 0 or Vo > Vcc)                                      | ±20 mA <u>2</u> / |

| Continuous output current (I <sub>O</sub> ) (V <sub>O</sub> = 0 to V <sub>CC</sub> ) | ±25 mA            |

| Continuous current through V <sub>CC</sub> or GND                                    | ±50 mA            |

| Storage temperature range (T <sub>STG</sub> )                                        |                   |

| Package thermal impedance (θ <sub>JA</sub> ): 3/                                     |                   |

| X package                                                                            | 86°C/W            |

| 9-                                                                                   |                   |

The package thermal impedance is calculated in accordance with JESD 51 7.

| DLA LAND AND MARITIME | SIZE | CAGE CODE | DWG NO.   |

|-----------------------|------|-----------|-----------|

|                       | A    | 16236     | V62/04697 |

| COLUMBUS, OHIO        |      | REV C     | PAGE 2    |

Stresses beyond those listed under "absolute maximum rating" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>2/</sup> The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

### 1.4 Recommended operating conditions. 4/ 5/

| Supply voltage range ( $V_{CC}$ )                                  | 4.5 V to 5.5 V           |

|--------------------------------------------------------------------|--------------------------|

| Input voltage range (Vi)                                           | 0.0 V to V <sub>CC</sub> |

| Output voltage range (Vo)                                          | 0.0 V to Vcc             |

| Minimum high level input voltage (V <sub>IH</sub> ):               |                          |

| V <sub>CC</sub> = 4.5 V to 5.5 V                                   | 2.0 V                    |

| Maximum low level input voltage (V <sub>IL</sub> ):                |                          |

| V <sub>CC</sub> = 4.5 V to 5.5 V                                   | 0.8 V                    |

| Maximum input transition rise or fall time ( $\Delta t/\Delta v$ ) | 500 ns                   |

| Operating free-air temperature range (T <sub>A</sub> )             | 40°C to +85°C            |

#### 2. APPLICABLE DOCUMENTS

## SOLID STATE TECHNOLOGY ASSOCIATION (JEDEC)

JEDEC PUB 95 - Registered and Standard Outlines for Semiconductor Devices

JESD 51-7 - High Effective Thermal Conductivity Test Board for Leaded Surface Mount Packages

(Copies of these documents are available online at https://www.jedec.org.)

#### 3. REQUIREMENTS

- 3.1 <u>Marking</u>. Parts shall be permanently and legibly marked with the manufacturer's part number as shown in 6.3 herein and as follows:

- A. Manufacturer's name, CAGE code, or logo

- B. Pin 1 identifier

- C. ESDS identification (optional)

- 3.2 <u>Unit container</u>. The unit container shall be marked with the manufacturer's part number and with items A and C (if applicable) above.

- 3.3 <u>Electrical characteristics</u>. The maximum and recommended operating conditions and electrical performance characteristics are as specified in 1.3, 1.4, and table I herein.

- 3.4 Design, construction, and physical dimension. The design, construction, and physical dimensions are as specified herein.

- 3.5 Diagrams.

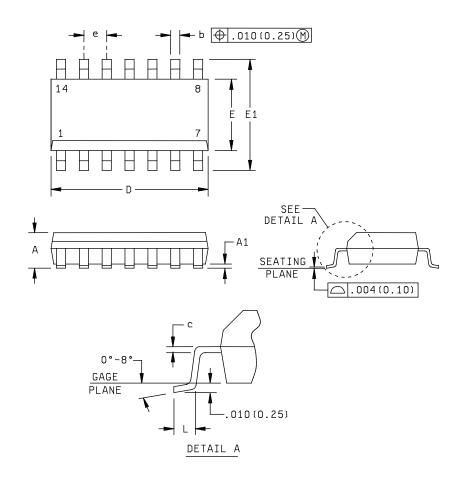

- 3.5.1 Case outline(s). The case outline(s) shall be as shown in 1.2.2 and figure 1.

- 3.5.2 Truth table. The truth table shall be as shown in figure 2.

- 3.5.3 Logic diagram. The logic diagram shall be as shown in figure 3.

- 3.5.4 Terminal connections. The terminal connections shall be as shown in figure 4.

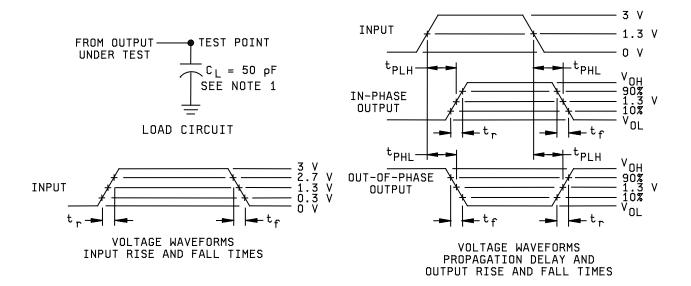

- 3.5.5 Test circuit and timing waveforms. The test circuit and timing waveforms shall be as shown in figure 5.

All unused inputs of the device must be held at  $V_{CC}$  or GND to ensure proper device operation.

<sup>5/</sup> Use of this product beyond the manufacturers design rules or stated parameters is done at the user's risk. The manufacturer and/or distributor maintain no responsibility or liability for product used beyond the stated limits.

| DLA LAND AND MARITIME | SIZE | CAGE CODE | DWG NO.   |

|-----------------------|------|-----------|-----------|

|                       | A    | 16236     | V62/04697 |

| COLUMBUS, OHIO        |      | REV C     | PAGE 3    |

TABLE I. Electrical performance characteristics. 1/

| Test                                             | Symbol             | Conditions                                                                      | V <sub>CC</sub>   | Temperature,           | Device<br>type |      |         | Unit |

|--------------------------------------------------|--------------------|---------------------------------------------------------------------------------|-------------------|------------------------|----------------|------|---------|------|

|                                                  |                    |                                                                                 |                   |                        |                | Min  | Max     |      |

| High level output voltage                        | V <sub>OH</sub>    | $V_I = V_{IH} \text{ or } V_{IL}  \underline{2}/I_{OH} = -20  \mu\text{A}$      | 4.5 V             | 25°C,<br>-40°C to 85°C | All            | 4.4  |         | V    |

|                                                  |                    | $V_I = V_{IH} \text{ or } V_{IL}  \underline{2}/I_{OH} = -4 \text{ mA}$         | 4.5 V             | 25°C                   |                | 3.98 |         |      |

|                                                  |                    |                                                                                 |                   | -40°C to 85°C          |                | 3.84 |         |      |

| Low level output voltage                         | VoL                | $V_I = V_{IH} \text{ or } V_{IL}  \underline{2}/$<br>$I_{OL} = 20  \mu\text{A}$ | 4.5 V             | 25°C,<br>-40°C to 85°C | All            |      | 0.1     | V    |

|                                                  |                    | $V_I = V_{IH} \text{ or } V_{IL}  \underline{2}/I_{OL} = 4 \text{ mA}$          | 4.5 V             | 25°C                   |                |      | 0.26    |      |

|                                                  |                    |                                                                                 |                   | -40°C to 85°C          |                |      | 0.33    |      |

| Input current                                    | lı                 | V <sub>I</sub> = V <sub>CC</sub> or 0 V                                         | 5.5 V             | 25°C                   | All            |      | ±100    | nA   |

|                                                  |                    |                                                                                 |                   | -40°C to 85°C          | -              |      | ±1000   |      |

| Quiescent supply current                         | Icc                | V <sub>I</sub> = V <sub>CC</sub> or 0 V                                         | 5.5 V             | 25°C                   | All            |      | 2.0     | μA   |

|                                                  |                    | I <sub>O</sub> = 0 A                                                            |                   | -40°C to 85°C          | -              |      | 20.0    |      |

| Quiescent supply current delta, TTL input levels | Δlcc<br><u>3</u> / | One input at 0.5 V or 2.4 V<br>Other inputs at 0.0 V or V <sub>CC</sub>         | 5.5 V             | 25°C                   | All            |      | 2.4     | mA   |

|                                                  |                    |                                                                                 |                   | -40°C to 85°C          |                |      | 2.9     |      |

| Input capacitance                                | Cı                 |                                                                                 | 4.5 V<br>to 5.5 V | 25°C,<br>-40°C to 85°C | All            |      | 10      | pF   |

| Power dissipation capacitance per inverter       | C <sub>PD</sub>    | No load                                                                         |                   | 25°C                   | All            | 20   | typical | pF   |

| Propagation delay time,<br>A to Y                | t <sub>pd</sub>    | C <sub>L</sub> = 50 pF<br>See figure 5                                          | 4.5 V             | 25°C                   |                |      | 20      | ns   |

|                                                  |                    |                                                                                 |                   | -40°C to 85°C          |                |      | 25      |      |

|                                                  |                    |                                                                                 | 5.5 V             | 25°C                   |                |      | 18      |      |

|                                                  |                    |                                                                                 |                   | -40°C to 85°C          |                |      | 23      |      |

| Output transition time                           | t <sub>t</sub>     |                                                                                 | 4.5 V             | 25°C                   |                |      | 15      | ns   |

|                                                  |                    |                                                                                 |                   | -40°C to 85°C          |                |      | 19      |      |

|                                                  |                    |                                                                                 | 5.5 V             | 25°C                   |                |      | 14      |      |

|                                                  |                    |                                                                                 |                   | -40°C to 85°C          |                |      | 17      |      |

Testing and other quality control techniques are used to the extent deemed necessary to assure product performance over the specified temperature range. Product may not necessarily be tested across the full temperature range and all parameters may not necessarily be tested. In the absence of specific parametric testing, product performance is assured by characterization and/or design.

$<sup>\</sup>frac{1}{2}$  This is the increase in supply current for each input that is at one of the specified TTL voltage levels, rather than 0.0 V or V<sub>CC</sub>.

| DLA LAND AND MARITIME | SIZE | CAGE CODE | DWG NO.   |

|-----------------------|------|-----------|-----------|

|                       | A    | 16236     | V62/04697 |

| COLUMBUS, OHIO        |      | REV C     | PAGE 4    |

<sup>2/</sup> The values to be used for V<sub>IH</sub> and V<sub>IL</sub> shall be the V<sub>IH</sub> minimum and V<sub>IL</sub> maximum values listed in section 1.4 herein.

| Dimensions |      |      |             |      |        |      |      |       |        |

|------------|------|------|-------------|------|--------|------|------|-------|--------|

| Symbol     | Inc  | hes  | Millimeters |      | Symbol | Inc  | hes  | Milli | meters |

|            | Min  | Max  | Min         | Max  |        | Min  | Max  | Min   | Max    |

| Α          |      | .069 |             | 1.75 | Е      | .150 | .157 | 3.81  | 4.00   |

| A1         | .004 | .010 | 0.10        | 0.25 | E1     | .228 | .244 | 5.80  | 6.20   |

| b          | .014 | .020 | 0.35        | 0.51 | е      | .050 | BSC  | 1.27  | BSC    |

| С          | .008 | NOM  | 0.20        | NOM  | L      | .016 | .044 | 0.40  | 1.12   |

| D          | .337 | .344 | 8.55        | 8.75 |        |      |      |       |        |

# NOTES:

- 1. All linear dimensions are in inches (millimeters).

- 2. This case outline is subject to change without notice.

- 3. Body dimensions do not include mold flash or protrusion, not to exceed .006 inches (0.15 millimeters).

- 4. Fall within JEDEC MS-012.

FIGURE 1. Case outline.

| DLA LAND AND MARITIME | SIZE | CAGE CODE | DWG NO.   |

|-----------------------|------|-----------|-----------|

|                       | A    | 16236     | V62/04697 |

| COLUMBUS, OHIO        |      | REV C     | PAGE 5    |

| Each inverter |             |  |  |

|---------------|-------------|--|--|

| Input<br>A    | Output<br>Y |  |  |

| Н             | L           |  |  |

| L             | Н           |  |  |

H = High voltage level L = Low voltage level

FIGURE 2. Truth table.

FIGURE 3. Logic diagram.

| Device type 01                                                  |     |    |     |  |  |

|-----------------------------------------------------------------|-----|----|-----|--|--|

| Case outlines: X                                                |     |    |     |  |  |

| Terminal Terminal Terminal Terminal number symbol number symbol |     |    |     |  |  |

| 1                                                               | 1A  | 8  | 4Y  |  |  |

| 2                                                               | 1Y  | 9  | 4A  |  |  |

| 3                                                               | 2A  | 10 | 5Y  |  |  |

| 4                                                               | 2Y  | 11 | 5A  |  |  |

| 5                                                               | 3A  | 12 | 6Y  |  |  |

| 6                                                               | 3Y  | 13 | 6A  |  |  |

| 7                                                               | GND | 14 | Vcc |  |  |

FIGURE 4. <u>Terminal connections</u>.

| DLA LAND AND MARITIME | SIZE | CAGE CODE | DWG NO.   |

|-----------------------|------|-----------|-----------|

|                       | A    | 16236     | V62/04697 |

| COLUMBUS, OHIO        |      | REV C     | PAGE 6    |

## NOTES:

- 1. C<sub>L</sub> includes probe and test-fixture capacitance.

- 2. Phase relationships between waveforms were chosen arbitrarily. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  1 MHz,  $Z_0$  = 50  $\Omega$ ,  $t_r$  = 6 ns,  $t_f$  = 6 ns.

- 3. The outputs are measured one at a time with one input transition per measurement.

- 4.  $t_{PLH}$  and  $t_{PHL}$  are the same as  $t_{pd}$ .

FIGURE 5. Test circuit and timing waveforms.

| DLA LAND AND MARITIME | SIZE | CAGE CODE | DWG NO.   |

|-----------------------|------|-----------|-----------|

|                       | A    | 16236     | V62/04697 |

| COLUMBUS, OHIO        |      | REV C     | PAGE 7    |

#### 4. VERIFICATION

4.1 <u>Product assurance requirements</u>. The manufacturer is responsible for performing all inspection and test requirements as indicated in their internal documentation. Such procedures should include proper handling of electrostatic sensitive devices, classification, packaging, and labeling of moisture sensitive devices, as applicable.

## 5. PREPARATION FOR DELIVERY

- 5.1 <u>Packaging</u>. Preservation, packaging, labeling, and marking shall be in accordance with the manufacturer's standard commercial practices for electrostatic discharge sensitive devices.

- 6. NOTES

- 6.1 ESDS. Devices are electrostatic discharge sensitive and are classified as ESDS class 1 minimum.

- 6.2 <u>Configuration control</u>. The data contained herein is based on the salient characteristics of the device manufacturer's data book. The device manufacturer reserves the right to make changes without notice. This drawing will be modified as changes are provided.

- 6.3 <u>Suggested source(s) of supply</u>. Identification of the suggested source(s) of supply herein is not to be construed as a guarantee of present or continued availability as a source of supply for the item. DLA Land and Maritime maintains an online database of all current sources of supply at <a href="https://landandmaritimeapps.dla.mil/programs/smcr/">https://landandmaritimeapps.dla.mil/programs/smcr/</a>.

| Vendor item drawing<br>administrative control<br>number <u>1</u> / | Device<br>manufacturer<br>CAGE code | Vendor part number | Top side<br>marking |

|--------------------------------------------------------------------|-------------------------------------|--------------------|---------------------|

| V62/04697-01XE                                                     | 01295                               | SN74HCT04IDREP     | SHCT04IEP           |

1/ The vendor item drawing establishes an administrative control number for identifying the item on the engineering documentation.

CAGE code Source of supply

01295 Texas Instruments, Inc.

Semiconductor Group

8505 Forest Lane

P.O. Box 660199 Dallas, TX 75243

| DLA LAND AND MARITIME | SIZE | CAGE CODE | DWG NO.   |

|-----------------------|------|-----------|-----------|

|                       | A    | 16236     | V62/04697 |

| COLUMBUS, OHIO        |      | REV C     | PAGE 8    |